Posts Tagged ‘възстановявам mcu data’

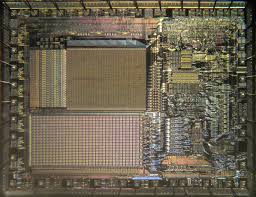

Attack Microcontroller W77E058A40DL Flash

Attack Microcontroller W77E058A40DL Flash

Attack Microcontroller W77E058A40DL Flash memory and disable the protective mechanism on it, extract firmware out from the MCU;

FEATURES

8-bit CMOS microcontroller

High speed architecture of 4 clocks/machine cycle runs up to 40 MHz

Pin compatible with standard 80C52

Instruction-set compatible with MCS-51

Four 8-bit I/O Ports

One extra 4-bit I/O port and Wait State control signal (available on 44-pin PLCC/QFP package)

Three 16-bit Timers when Attack Microcontroller

12 interrupt sources with two levels of priority

On-chip oscillator and clock circuitry

Two enhanced full duplex serial ports

32 KB Flash EPROM

256 bytes scratch-pad RAM

1 KB on-chip SRAM for MOVX instruction

Programmable Watchdog Timer

Dual 16-bit Data Pointers after Attack Microcontroller

Software programmable access cycle to external RAM/peripherals

Packages:

− Lead Free(RoHS) DIP 40:

W77E058A40DL

− Lead Free(RoHS) PLCC 44: W77E058A40PL

− Lead Free(RoHS) PQFP 44: W77E058A40FL if Attack Microcontroller

GENERAL DESCRIPTION

The W77E058 is a fast 8051 compatible microcontroller with a redesigned processor core without

wasted clock and memory cycles. As a result, it executes every 8051 instruction faster than the

original 8051 for the same crystal speed. Typically, the instruction executing time of W77E058 is 1.5 to 3 times faster then that of traditional 8051, depending on the type of instruction when Attack Microcontroller. In general, the overall performance is about 2.5 times better than the original for the same crystal speed. Giving the same throughput with lower clock speed, power consumption has been improved. Consequently, the W77E058 is a fully static CMOS design; it can also be operated at a lower crystal clock. The W77E058 contains 32 KB Flash EPROM, and provides operating voltage from 4.5V to 5.5V before Attack Microcontroller. All W77E058 types also support on-chip 1 KB SRAM without external memory component and glue logic, saving more I/O pins for users’ application usage if they use on-chip SRAM instead of external SRAM.