Posts Tagged ‘złamać wiór code’

Break IC MC9S12XDG128 Heximal

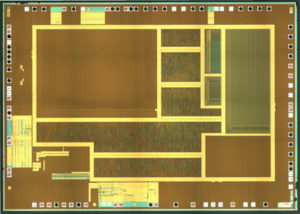

Break IC MC9S12XDG128 Heximal

We can Break IC MC9S12XDG128 Heximal, please view below IC MC9S12XDG128 features for your reference:

Introduction

Targeted at automotive multiplexing applications, the MC9S12XD Family will deliver 32-bit performance with all the advantages and efficiencies of a 16-bit MCU. The S12X is designed to retain the low cost, low power consumption, excellent EMC performance and code-size efficiency advantages enjoyed by users of Freescale’s previous 16-bit MC9S12 MCU family.

Based around an enhanced S12 core, the MC9S12XD Family will deliver two to five times the performance of a 25 MHz S12 whilst retaining a high degree of pin and code compatibility with the original S12D – family.

The MC9S12XD Family features the performance boosting XGATE co-processor. The XGATE, which is programmable in “C” language, has an instruction set which is optimized for data movement, logic and bit manipulation instructions. It runs at twice the bus frequency of the S12X and off-loads the CPU by providing high speed data transfer (and data processing) between any peripheral module, RAM and I/O ports before Break IC. This is particularly useful in applications such as automotive gateways where there are multiple busses carrying heavy data traffic which would otherwise exert a heavy interrupt/processing load on the CPU.

The MC9S12XD Family will feature an enhanced MSCAN module which, when used in conjunction with XGATE, delivers FullCAN performance with virtually unlimited number of mailboxes and retains backwards compatibility with the MSCAN module featured on previous S12 products.

Memory options will range from 64 Kbytes to 512 Kbytes of Freescale’s industry-leading, full automotive spec SG-Flash with additional integrated EEPROM.

In addition to the rich S12 peripheral set, the MC9S12XD Family will feature more RAM, extra A/D channels, new timer features and additional LIN-compatible SCI ports compared with the original S12 D Family. The MC9S12XD Family also features a new flexible interrupt handler which allows multilevel nested interrupts.

The MC9S12XD Family has full 16-bit data paths throughout. The non-multiplexed expanded bus interface available on the 144-pin versions allows an easy interface to external memories. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to suit operational requirements. System power consumption is further improved with the new “fast exit from STOP mode” feature and an ultra low power wakeup timer.

In addition to the I/O ports available in each module, up to 25 further I/O ports are available with interrupt capability allowing wakeup from STOP or WAIT mode.

The MC9S12XD Family will be available in 144-pin LQFP (with optional external bus), 112-pin, and 80-pin options.