Posts Tagged ‘rupe fișier software protejat pentru microcomputer’

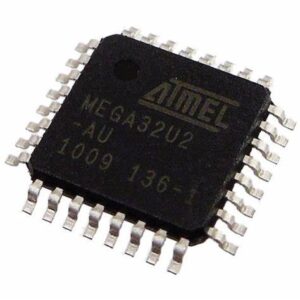

Break ATMEGA32U2-AU Microcontroller Flash Memory

Break ATMEGA32U2-AU Microcontroller Flash Memory

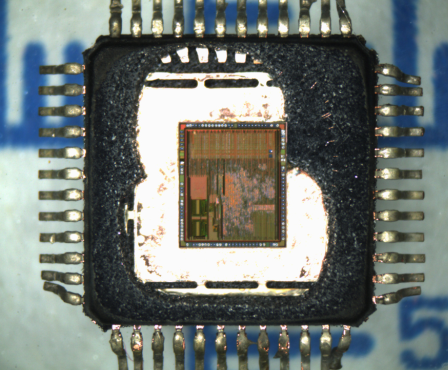

Break ATMEGA32U2-AU Microcontroller Flash Memory and clone microprocessor memory data to new atmega32u2 chip, the embedded software will be readout from mcu atmega32u2;

This is set up as indicated in the specification for the MCU Control Register – MCUCR. When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low.

Note that recognition of falling or rising edge interrupts on INT0 and INT1 requires the presence of an I/O clock when reverse engineering atmel avr chip atmega32a program file, described in “Clock Systems and their Distribution”.

Low level interrupts on INT0/INT1 are detected asynchronously. This implies that these interrupts can be used for waking the part also from sleep modes other than Idle mode. The I/O clock is halted in all sleep modes except Idle mode.

quebrar ATMEGA32U2-AU microcontrolador de memória flash e clonar dados de memória de microprocessador para o novo chip atmega32u2, o software incorporado será lido a partir de mcu atmega32u2

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU in the process of recover protected atmega32 mcu memory. This makes the MCU less sensitive to noise. The changed level is sampled twice by the Watchdog Oscillator clock.