Posts Tagged ‘reverse Microchip PIC18F4515’

Microchip PIC18F4515 Embedded Firmware Restoration

Microchip PIC18F4515 Embedded Firmware Restoration

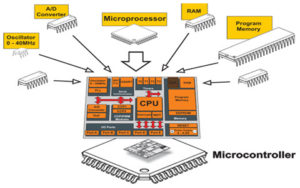

Microchip PIC18F4515 Embedded Firmware Restoration is a process to extract the embedded heximal from PIC18F4515 after crack microcontroller PIC18F4515 protection system;

The instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely due to the process of Attack Microcontroller W77E058A40DL Flash. Using this “forced” addressing allows the instruction to operate on a data address in a single cycle which will facilitate Microchip PIC18F4515 Embedded Firmware Restoration, without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently.

فك تشفير فلاش المعالج الدقيق PIC18F4515 هو عملية لإزالة آلية مقاومة العبث لذاكرة فلاش PIC18F4515 المؤمنة وذاكرة eeprom، ونسخ البرامج الثابتة المضمنة لوحدة التحكم الدقيقة PIC18F4515 المقفلة للبرنامج الثنائي أو البيانات السداسية إلى نسخة أخرى من MCU PIC18F4515 والتي ستوفر نفس وظائف الإصدار الأصلي

The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables by Attack MCU ATMEGA162 Flash. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 5.5.3 “Mapping the Access Bank in Indexed Literal Offset Mode”.

PIC18F4515 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow downwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device when Microchip PIC18F4515 Embedded Firmware Restoration. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top half of Bank 15 (F80h to FFFh).

Dekodowanie flash mikroprocesora PIC18F4515 to proces mający na celu usunięcie mechanizmu zabezpieczającego przed manipulacją zabezpieczonej pamięci flash mikrochipu PIC18F4515 i pamięci eeprom, kopiowanie zablokowanego oprogramowania układowego mikrokontrolera PIC18F4515 wbudowanego programu binarnego lub danych szesnastkowych do innego klona MCU PIC18F4515, który zapewni te same funkcje co wersja oryginalna

The SFRs can be classified into two sets: those associated with the “core” device functionality (ALU, Resets and interrupts) and those related to the peripheral functions obtained from Copy MCU AT89C55WD Binary. The Reset and Interrupt registers are described in their respective chapters, while the ALU’s STATUS register is described later in this section.

Registers related to the operation of a peripheral feature are described in the chapter for that peripheral. The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as ‘0’s to Crack MCU.

Флаш декодирането на микропроцесор PIC18F4515 на микрочип е процес за премахване на механизма за защита срещу фалшифициране на защитен микрочип PIC18F4515 флаш памет и eeprom памет, копиране на заключен микроконтролер PIC18F4515, вграден фърмуер на двоична програма или шестнадесетични данни в друг клонинг MCU PIC18F4515, който ще осигури същите функции като оригиналната версия