Posts Tagged ‘Reverse Engineering Microcontroller locked program’

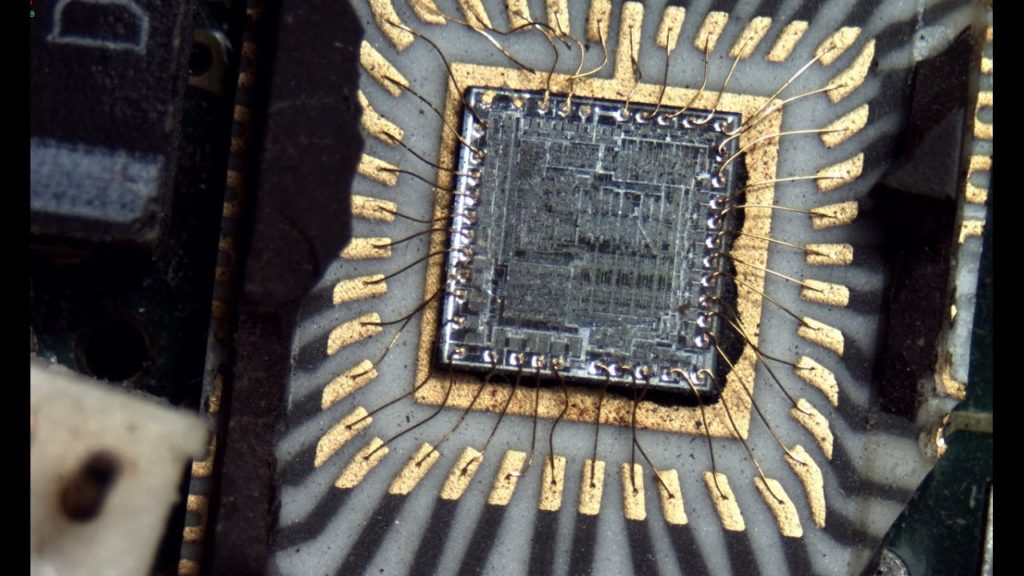

Reverse Engineering Microcontroller ATMEGA1281 Program

Reverse Engineering Microcontroller ATMEGA1281 Program

Reverse Engineering Microcontroller ATMEGA1281 purpose is to unlock mcu atmega1281 flash memory and then copy Program and data from atmega1281 memory to new MCU;

Features

High Performance, Low Power AVR® 8-Bit Microcontroller

Advanced RISC Architecture

– 135 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-Chip 2-cycle Multiplier

Non-volatile Program and Data Memories

– 64K/128K/256K Bytes of In-System Self-Programmable Flash

Endurance: 10,000 Write/Erase Cycles

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– 4K Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

– 8K Bytes Internal SRAM

– Up to 64K Bytes Optional External Memory Space

– Programming Lock for Software Security

JTAG (IEEE std. 1149.1 compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support when copy cpld epm9320arc208

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

– Four 16-bit Timer/Counter with Separate Prescaler, Compare- and Capture Mode

– Real Time Counter with Separate Oscillator

– Four 8-bit PWM Channels

– Six/Twelve PWM Channels with Programmable Resolution from 2 to 16 Bits (ATmega1281/2561, ATmega640/1280/2560)

– Output Compare Modulator

– 8/16-channel, 10-bit ADC

– Two/Four Programmable Serial USART (ATmega1281/2561,ATmega640/1280/2560)

– Master/Slave SPI Serial Interface

– Byte Oriented 2-wire Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator after Reverse engineering Microcontroller

– On-chip Analog Comparator

– Interrupt and Wake-up on Pin Change

Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated Oscillator

– External and Internal Interrupt Sources when Reverse engineering Microcontroller

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and Extended Standby

I/O and Packages

– 51/86 Programmable I/O Lines (ATmega1281/2561, ATmega640/1280/2560)

– 64-lead (ATmega1281/2561)

– 100-lead (ATmega640/1280/2560)

– 100-lead TQFP (64-lead TQFP Option)

Temperature Range:

– -40°C to 85°C Industrial if Reverse engineering Microcontroller

Speed Grade:

Programmable Flash

– ATmega1281/2561V/ATmega640/1280/2560V: 0 – 4 MHz @ 1.8 – 5.5V, 0 – 8 MHz @ 2.7 – 5.5V

– ATmega640/1280/1281/2560/2561: 0 – 8 MHz @ 2.7 – 5.5V, 0 – 16 MHz @ 4.5 – 5.5V before Reverse engineering Microcontroller

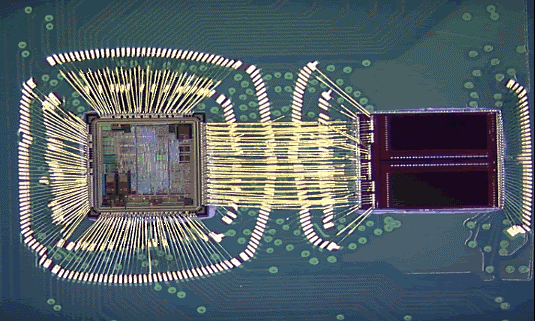

Reverse Engineering Microcontroller ATmega640

Reverse Engineering Microcontroller ATmega640

Reverse Engineering Microcontroller ATmega640 and readout the embedded content from mcu atmega640, atmega640 mcu protection can be unlocked by focus ion beam;

Features

High Performance, Low Power AVR® 8-Bit Microcontroller

Advanced RISC Architecture

– 135 Powerful Instructions – Most Single Clock Cycle Execution when copy pic18f252 Microcontroller

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-Chip 2-cycle Multiplier

High Endurance Non-volatile Memory Segments

– 64K/128K/256K Bytes of In-System Self-Programmable Flash

– 4K Bytes EEPROM

– 8K Bytes Internal SRAM

– Write/Erase Cycles:10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85°C/ 100 years at 25°C

– Optional Boot Code Section with Independent Lock Bits after recover dspic30f6013a Microcontroller

In-System Programming by On-chip Boot Program

True Reverse engineering-While-Write Operation

– Programming Lock for Software Security

Endurance: Up to 64K Bytes Optional External Memory Space

JTAG (IEEE std. 1149.1 compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

– Four 16-bit Timer/Counter with Separate Prescaler, Compare- and Capture Mode

– Real Time Counter with Separate Oscillator

– Four 8-bit PWM Channels

– Six/Twelve PWM Channels with Programmable Resolution from 2 to 16 Bits

(ATmega1281/2561, ATmega640/1280/2560)

– Output Compare Modulator

– 8/16-channel, 10-bit ADC (ATmega1281/2561, ATmega640/1280/2560) after Reverse engineering Microcontroller

– Two/Four Programmable Serial USART (ATmega1281/2561,ATmega640/1280/2560)

– Master/Slave SPI Serial Interface

– Byte Oriented 2-wire Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

– Interrupt and Wake-up on Pin Change

Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated Oscillator

– External and Internal Interrupt Sources

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and Extended Standby I/O and Packages

– 54/86 Programmable I/O Lines (ATmega1281/2561, ATmega640/1280/2560)

– 64-pad QFN/MLF, 64-lead TQFP (ATmega1281/2561)

– 100-lead TQFP, 100-ball CBGA (ATmega640/1280/2560)

– RoHS/Fully Green

Temperature Range:

– -40°C to 85°C Industrial

Ultra-Low Power Consumption

– Active Mode: 1 MHz, 1.8V: 500 µA

– Power-down Mode: 0.1 µA at 1.8V

Speed Grade:

– ATmega640V/ATmega1280V/ATmega1281V:

0 – 4 MHz @ 1.8 – 5.5V, 0 – 8 MHz @ 2.7 – 5.5V

– ATmega2560V/ATmega2561V:

0 – 2 MHz @ 1.8 – 5.5V, 0 – 8 MHz @ 2.7 – 5.5V

– ATmega640/ATmega1280/ATmega1281:

0 – 8 MHz @ 2.7 – 5.5V, 0 – 16 MHz @ 4.5 – 5.5V

– ATmega2560/ATmega2561:

0 – 16 MHz @ 4.5 – 5.5V

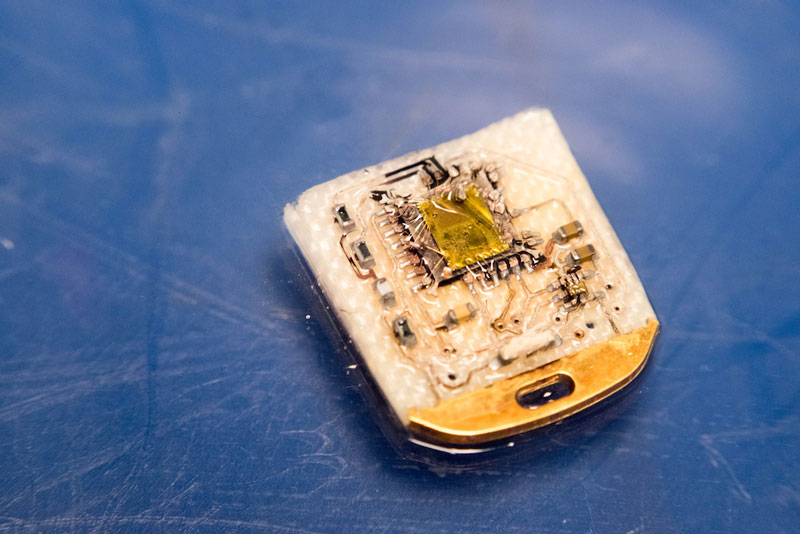

Reverse Engineering Microcontroller ATtiny461 Code

Reverse Engineering Microcontroller ATtiny461 Code

Reverse Engineering Microcontroller ATtiny461 and find out the fuse bit of it, in order to extract Code from mcu attiny461, and crack microcontroller attiny461 by focus ion beam technique to get the flash and eeprom memory decapped;

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle.

The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATtiny261/461/861 provides the following features: 2/4/8K byte of In-System Programmable Flash, 128/256/512 bytes EEPROM, 128/256/512 bytes SRAM, 6 general purpose I/O lines, 32 general purpose working registers, one 8-bit Timer/Counter with compare modes, one 8-bit high speed Timer/Counter, Universal Serial Interface, Internal and External Interrupts, a 4-channel, 10-bit ADC, a programmable Watchdog Timer with internal Oscillator, and three software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counter, ADC, Analog Comparator, and Interrupt system to continue functioning.

The Power-down mode saves the register contents, disabling all chip functions until the next Interrupt or Hardware Reset. The ADC Noise Reduction mode stops the CPU and all I/O modules except ADC, to minimize switching noise during ADC conversions if Recover mcu at89c4051 heximal.

The fast-access register file concept contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This means that during one single clock cycle, one ALU (Arithmetic Logic Unit) operation is executed. Two operands are output from the register file, the operation is executed, and the result is stored back in the register file – in one clock cycle.

Six of the 32 registers can be used as three 16-bits indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the three address pointers is also used as the address pointer for the constant table look up function after Recover 430g2452 Microcontroller heximal.

These added function registers are the 16-bits X-register, Y-register and Z-register. The ALU supports arithmetic and logic functions between registers or between a constant and a register. Single register operations are also executed in the ALU.

Figure 4 shows the AT90S2313 AVR Enhanced RISC microcontroller architecture. In addition to the register operation, the conventional memory addressing modes can be used on the register file as well. This is enabled by the fact that the register file is assigned the 32 lowermost Data Space addresses ($00 – $1F), allowing them to be accessed as though they were ordinary memory locations before break LPC2132FBD64 firmware.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, Timer/Counters, A/D-converters, and other I/O functions. The I/O memory can be accessed directly, or as the Data Space locations following those of the register file, $20 – $5F.

The device is manufactured using Atmel’s high density non-volatile memory technology. The On-chip ISP Flash allows the Program memory to be re-programmed In-System through an SPI serial interface, by a conventional non-volatile memory programmer or by an On-chip boot code running on the AVR core.

The ATtiny261/461/861 AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-Circuit Emulators, and Evaluation kits.