Posts Tagged ‘reverse engineering IC protected binary’

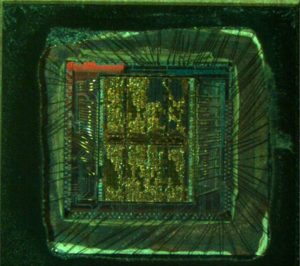

Reverse Engineering IC ATmega644A Firmware

Reverse Engineering IC ATmega644A Firmware

Reverse Engineering IC ATmega644A and clone ATmega644A microcontroller firmware from embedded flash and eeprom memory;

If the On-chip debug system is enabled by the OCDEN Fuse and the chip enters sleep mode, the main clock source is enabled, and hence, always consumes power. In the deeper sleep modes, this will contribute significantly to the total current consumption.

There are three alternative ways to disable the OCD system: Disable the OCDEN Fuse. Disable the JTAGEN Fuse. Write one to the JTD bit in MCUCR.

During reset, all I/O Registers are set to their initial values, and the program starts execution from the Reset Vector. The instruction placed at the Reset Vector must be a JMP – Absolute Jump – instruction to the reset handling routine.

If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program firmware can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa before attack microcontroller mc68hc705p6 bin.

The circuit diagram in Figure 25 shows the reset logic. Table 23 defines the electrical parameters of the reset circuitry. The I/O ports of the AVR are immediately reset to their initial state when a reset source goes active. This does not require any clock source to be running if attack chip st62t00cb6 firmware.

After all reset sources have gone inactive, a delay counter is invoked, stretching the internal reset. This allows the power to reach a stable level before normal operation starts. The time-out period of the delay counter is defined by the user through the SUT and CKSEL Fuses. The different selections for the delay period are presented in “Clock Sources”.

The ATmega644 has five sources of reset: Power-on Reset. The MCU is reset when the supply voltage is below the Power-on Reset threshold (VPOT). External Reset. The MCU is reset when a low level is present on the RESET pin for longer than the minimum pulse length before copy mcu pic18f2480 program.

Watchdog Reset. The MCU is reset when the Watchdog Timer period expires and the Watchdog is enabled. Brown-out Reset. The MCU is reset when the supply voltage VCC is below the Brown-out Reset threshold (VBOT) and the Brown-out Detector is enabled.

JTAG AVR Reset. The MCU is reset as long as there is a logic one in the Reset Register, one of the scan chains of the JTAG system. Refer to the section “IEEE 1149.1 (JTAG) Boundary-scan” on page 301 for details.

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detection level is defined in Table 23. The POR is activated whenever VCC is below the detection level. The POR circuit can be used to trigger the start-up Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in RESET after VCC rise. The RESET signal is activated again, without any delay, when VCC decreases below the detection level.

An External Reset is generated by a low level on the RESET pin. Reset pulses longer than the minimum pulse width (see Table 23) will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage – VRST – on its positive edge, the delay counter starts the MCU after the Time-out period – tTOUT – has expired.

ATmega644 has an On-chip Brown-out Detection (BOD) circuit for monitoring the VCC level during operation by comparing it to a fixed trigger level. The trigger level for the BOD can be selected by the BODLEVEL Fuses. The trigger level has a hysteresis to ensure spike free Brown-out Detection. The hysteresis on the detection level should be interpreted as VBOT+ = VBOT + VHYST/2 and VBOT- = VBOT – VHYST/2.

Reverse Engineering IC PIC18F248 Binary

Reverse Engineering IC PIC18F248 Binary

Reverse Engineering IC PIC18F248 and locate the fuse bit position, crack mcu pic18f248 flash memory by focus ion beam and copy the embedded firmware from microcontroller pic18f248;

High-Performance RISC CPU:

· Linear program memory addressing up to 2 Mbytes

· Linear data memory addressing to 4 Kbytes

· Up to 10 MIPS operation

· DC – 40 MHz clock input

· 4 MHz-10 MHz oscillator/clock input with PLL active when copy microcontroller pic16f737 flash memory

· 16-bit wide instructions, 8-bit wide data path

· Priority levels for interrupts

· 8 x 8 Single-Cycle Hardware Multiplier

Peripheral Features:

· High current sink/source 25 mA/25 mA

· Three external interrupt pins

· Timer0 module: 8-bit/16-bit timer/counter with 8-bit programmable prescaler

· Timer1 module: 16-bit timer/counter

· Timer2 module: 8-bit timer/counter with 8-bit period register (time base for PWM)

· Timer3 module: 16-bit timer/counter

· Secondary oscillator clock option – Timer1/Timer3

· Capture/Compare/PWM (CCP) modules; CCP pins can be configured as:

– Capture input: 16-bit, max resolution 6.25 ns

– Compare: 16-bit, max resolution 100 ns (TCY) before break mcu pic18f442 software

– PWM output: PWM resolution is 1 to 10-bit Max. PWM freq. @:8-bit resolution = 156 kHz 10-bit resolution = 39 kHz

· Enhanced CCP module which has all the features of the standard CCP module, but also has the following features for advanced motor control:

– 1, 2 or 4 PWM outputs

– Selectable PWM polarity

– Programmable PWM dead time

· Master Synchronous Serial Port (MSSP) with two modes of operation:

– 3-wire SPI™ (Supports all 4 SPI modes) after Reverse engineering IC

– I2C™ Master and Slave mode

· Addressable USART module:

– Supports interrupt-on-address bit

Advanced Analog Features:

· 10-bit, up to 8-channel Analog-to-Digital Converter module (A/D) with:

– Conversion available during Sleep

– Up to 8 channels available

· Analog Comparator module:

– Programmable input and output multiplexing

· Comparator Voltage Reference module

· Programmable Low-Voltage Detection (LVD) module:

– Supports interrupt-on-Low-Voltage Detection

· Programmable Brown-out Reset (BOR)

CAN bus Module Features:

· Complies with ISO CAN Conformance Test

· Message bit rates up to 1 Mbps

· Conforms to CAN 2.0B Active Spec with:

– 29-bit Identifier Fields

– 8-byte message length

– 3 Transmit Message Buffers with prioritization

– 2 Receive Message Buffers

– 6 full, 29-bit Acceptance Filters

– Prioritization of Acceptance Filters

– Multiple Receive Buffers for High Priority Messages to prevent loss due to overflow

– Advanced Error Management Features

Special Microcontroller Features:

· Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Watchdog Timer (WDT) with its own on-chip RC oscillator

· Programmable code protection

· Power-saving Sleep mode

· Selectable oscillator options, including:

– 4x Phase Lock Loop (PLL) of primary oscillator

– Secondary Oscillator (32 kHz) clock input

· In-Circuit Serial ProgrammingTM (ICSPTM) via two pins IC Flash Technology:

· Low-power, high-speed Enhanced Flash technology

· Fully static design Wide operating voltage range (2.0V to 5.5V) Industrial and Extended temperature ranges