Posts Tagged ‘recover chip embedded content’

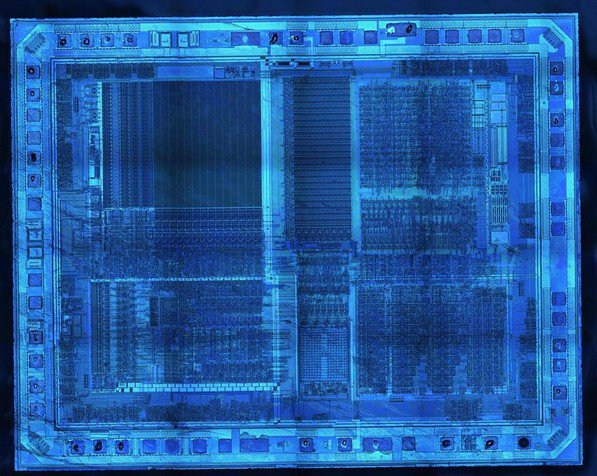

Recover Chip PIC16F689 Flash

Recover Chip PIC16F689 Flash

We can Recover Chip PIC16F689 Flash, please view the CHIP PIC16F689 features below for your reference:

High-Performance RISC CPU:

· Only 35 Instructions to Learn:

– All single-cycle instructions except branches

· Operating Speed:

– DC – 20 MHz oscillator/clock input

– DC – 200 ns instruction cycle

· Interrupt Capability

· 8-level Deep Hardware Stack

Low-Power Features:

· Standby Current:

– 50 nA @ 2.0V, typical

· Operating Current:

– 11 ìA @ 32 kHz, 2.0V, typical

– 220 ìA @ 4 MHz, 2.0V, typical

· Watchdog Timer Current:

– 1 ìA @ 2.0V, typical

· Direct, Indirect and Relative Addressing modes

Peripheral Features:

Special Microcontroller Features:

· Precision Internal Oscillator:

– Factory calibrated to ±1%

– Software selectable frequency range of 8 MHz to 125 kHz

– Software tunable

– Two-Speed Start-Up mode

– Crystal fail detect for critical applications

– Clock mode switching during operation for power savings

· Power-Saving Sleep mode

· Wide Operating Voltage Range (2.0V-5.5V)

· Industrial and Extended Temperature Range

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Brown-out Reset (BOR) with Software Control Option

· Enhanced Low-Current Watchdog Timer (WDT) with on-chip oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

· Multiplexed Master Clear with Weak Pull-up or Input Only Pin

· Programmable Code Protection

· High-Endurance Flash/EEPROM Cell:

– 100,000 write Flash endurance

– 1,000,000 write EEPROM endurance

– Flash/Data EEPROM retention: > 40 years

· 12 I/O Pins with Individual Direction Control:

– High-current source/sink for direct LED drive

– Interrupt-on-change pin

– Individually programmable weak pull-ups

– Ultra Low-Power Wake-up

· Analog Comparator module with:

– Two analog comparators

– Programmable On-chip Voltage Reference (CVREF) module (% of VDD)

– Comparator inputs and outputs externally accessible

· A/D Converter:

– 10-bit resolution and 8 channels

· Timer0: 8-bit Timer/Counter with 8-bit Programmable Prescaler

· Enhanced Timer1:

– 16-bit timer/counter with prescaler

– External Timer1 Gate (count enable)

– Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

· Enhanced USART Module:

– Supports RS-485, RS-232, LIN 2.0/2.1 and J2602

– Auto-Baud Detect

– Auto-wake-up on Start bit

· In-Circuit Serial Programming™ (ICSP™) via two pins

Recover Chip ATmega261A Program

Recover Chip ATmega261A Program

Recover Chip ATmega261A means the program of MCU ATmega261A from flash memory and eeprom memory will be readout and fuse bit of Microcontroller ATmega261A will be unlocked;

There are basically two types of interrupts. The first type is triggered by an event that sets the Interrupt Flag. For these interrupts, the Program Counter is vectored to the actual Interrupt Vector in order to execute the interrupt handling routine, and hardware clears the corresponding Interrupt Flag.

Interrupt Flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared. If an interrupt condition occurs while the corresponding interrupt enable bit is cleared, the Interrupt Flag will be set and remembered until the interrupt is enabled, or the flag is cleared by software if break mcu atmega64pa binary.

Similarly, if one or more interrupt conditions occur while the Global Interrupt Enable bit is cleared, the corresponding Interrupt Flag(s) will be set and remembered until the Global Interrupt Enable bit is set, and will then be executed by order of priority.

The second type of interrupts will trigger as long as the interrupt condition is present. These interrupts do not necessarily have Interrupt Flags. If the interrupt condition disappears before the interrupt is enabled, the interrupt will not be triggered after break ic atmega128a firmware.

When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served. Note that the Status Register is not automatChipally stored when entering an interrupt routine, nor restored when returning from an interrupt routine.

This must be handled by software. When using the CLI instruction to disable interrupts, the interrupts will be immediately disabled. No interrupt will be executed after the CLI instruction, even if it occurs simultaneously with the CLI instruction. The following example shows how this can be used to avoid interrupts during the timed EEPROM write sequence.

The interrupt execution response for all the enabled AVR interrupts is five clock cycles minimum. After five clock cycles the program vector address for the actual interrupt handling routine is executed. During these five clock cycle period, the Program Counter is pushed onto the Stack when Recover ic atmega168pa program.

The vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by five clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes five clock cycles. During these five clock cycles, the Program Counter (three bytes) is popped back from the Stack, the Stack Pointer is incremented by three, and the I-bit in SREG is set.