Posts Tagged ‘recouvrer circuit intégré program’

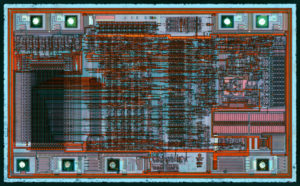

Copy MCU PIC16F916 Binary

Copy MCU PIC16F916 Binary

Copy MCU PIC16F916 Binary and reprograme the firmware to new microcontroller, crack MCU PIC16F916 security fuse bit and the flash content can be readout from microprocessor PIC16F916.

DEVICE OVERVIEW

The PIC16F91X/946 devices are covered by this datasheet. They are available in 28/40/44/64-pin packages. Figure 1-1 shows a block diagram of the PIC16F913/916 device, Figure 1-2 shows a block diagram of the PIC16F914/917 device, and Figure 1-3 shows a block diagram of the PIC16F946 device. Table 1-1 shows the pinout descriptions.

MEMORY ORGANIZATION

The PIC16F91X/946 has a 13-bit program counter capable of addressing a 4K x 14 program memory space for the PIC16F913/914 (0000h-0FFFh) and an 8K x 14 program memory space for the PIC16F916/917 and PIC16F946 (0000h-1FFFh). Accessing a location above the memory boundaries for the PIC16F913 and PIC16F914 will cause a wrap around within the first 4K x 14 space. The Reset vector is at 0000h and the interrupt vector is at 0004h after attack microcontroller pic18f66k90 heximal.

DATA MEMORY ORGANIZATION

The data memory is partitioned into multiple banks which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). Bits RP0 and RP1 are bank select bits.

Bank 0 is selected

Bank 1 is selected

Bank 2 is selected

Bank 3 is selected

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank are mirrored in another bank for code reduction and quicker access.

2.2.1

GENERAL PURPOSE REGISTER

The register file is organized as 256 x 8 bits in the PIC16F913/914, 352 x 8 bits in the PIC16F916/917 and 336 x 8 bits in the PIC16F946. Each register is accessed either directly or indirectly through the File Select for the purpose of Copy MCU pic18f458 binary

Register (FSR) (see Section 2.5 “Indirect Addressing, INDF and FSR Registers”).

SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Tables 2-1, 2-2, 2-3 and 2-4). These registers are static RAM.

The Special Function Registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the “core” are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.