Posts Tagged ‘quebrar ic flash’

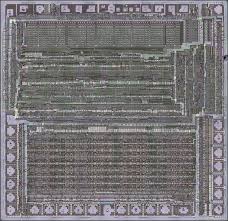

Break MCU dsPIC30F4011 Heximal

Break MCU dsPIC30F4011 Heximal

Break MCU dsPIC30F4011 memory and extract its Heximal out from its flash and eeprom, clone firmware to blank Microcontroller dsPIC30F4011 which will provide the same functions as original IC Clone;

Peripheral Features:

this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the “dsPIC30F Family Reference Manual” (DS70046). For more information on the device instruction set and programming, refer to the “16-bit MCU and DSC Reference Manual” (DS70157).

High-Performance, Modified RISC CPU:

· Modified Harvard architecture

· C compiler optimized instruction set architecture with flexible addressing modes

· 83 base instructions

· 24-bit wide instructions, 16-bit wide data path

· 48 Kbytes on-chip Flash program space (16K instruction words)

· 2 Kbytes of on-chip data RAM

· 1 Kbyte of nonvolatile data EEPROM

· Up to 30 MIPS operation:

– DC to 40 MHz external clock input

– 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

· 30 interrupt sources:

– Three external interrupt sources

– Eight user-selectable priority levels for each

· High-current sink/source I/O pins: 25 mA/25 mA

· Timer module with programmable prescaler:

– Five 16-bit timers/counters; optionally pair 16-bit timers into 32-bit timer modules

· 16-bit Capture input functions

· 16-bit Compare/PWM output functions

· 3-wire SPI modules (supports 4 Frame modes)

· I2C™ module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

· Two UART modules with FIFO Buffers

· CAN module, 2.0B compliant

Motor Control PWM Module Features:

· Six PWM output channels:

– Complementary or Independent Output modes

– Edge and Center-Aligned modes

· Three duty cycle generators

· Dedicated time base

· Programmable output polarity

· Dead-time control for Complementary mode

· Manual output control

· Trigger for A/D conversions

Quadrature Encoder Interface Module Features:

interrupt source

– Four processor trap sources

· 16 x 16-bit working register array

Phase A, Phase B and Index Pulse input 16-bit up/down position counter

Count direction status

Position Measurement (x2 and x4) mode

Programmable digital noise filters on inputs

Dual data fetch

Accumulator write-back for DSP operations

Alternate 16-bit Timer/Counter mode

Interrupt on position counter rollover/underflow

Modulo and Bit-Reversed Addressing modes

Two, 40-bit wide accumulators with optional saturation logic

Analog Features:

· 17-bit x 17-bit single-cycle hardware fractional/integer multiplier

· All DSP instructions are single cycle

· ±16-bit, single-cycle shift

· 10-bit Analog-to-Digital Converter (ADC) with four Sample and Holde (S&H) inputs:

– 1 Msps conversion rate

– Nine input channels

– Conversion available during Sleep and Idle

· Programmable Brown-out Reset only