Posts Tagged ‘kopie mcu bin’

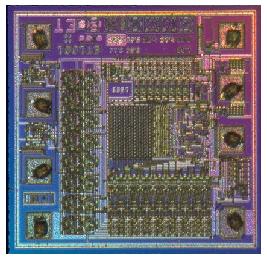

Break PLD PALCE16V8H-15JC Software

Break PLD PALCE16V8H-15JC Software

Break PLD PALCE16V8H-15JC and extract Software from PALCE16V8 pld memory, copy JED file to new PLD chip;

We can Break PLD PALCE16V8H-15JC Software, please view below PLD PALCE16V8H-15JC features for your reference:

DISTINCTIVE CHARACTERISTICS

Pin and function compatible with all 20-pin GAL devices

Electrically erasable CMOS technology provides reconfigurable logic and full testability

High-speed CMOS technology

— 5-ns propagation delay for “-5” version

— 7.5-ns propagation delay for “-7” version

Direct plug-in replacement for the PAL16R8 series and most of the PAL10H8 series

Outputs programmable as registered or combinatorial in any combination, Peripheral Component Interconnect (PCI) compliant if recover pic16c554 software

GENERAL DESCRIPTION

The PALCE16V8 is an advanced PAL device built with low-power, high-speed, electrically-erasable CMOS technology. It is functionally compatible with all 20-pin GAL devices. The macrocells provide a universal device architecture.

The PALCE16V8 will directly replace the PAL16R8 and PAL10H8 series devices, with the excep-

tion of the PAL16C1.

The PALCE16V8 utilizes the familiar sum-of-products (AND/OR) architecture that allows users to implement complex logic functions easily and efficiently. Multiple levels of combinatorial logic can always be reduced to sum-of-products form, taking advantage of the very wide input gates available in PAL devices after recover microcontroller pic16f83 eeprom.

The equations are programmed into the device through floating gate cells in the AND logic array that can be erased electrically.

Programmable output polarity

Programmable enable/disable control

Preloadable output registers for testability

Automatic register reset on power up

Cost-effective 20-pin plastic DIP, PLCC, and SOIC packages

Extensive third-party software and programmer support through FusionPLD partners

Fully tested for 100% programming and functional yields and high reliability

5 ns version utilizes a split leadframe for improved performance.

The fixed OR array allows up to eight data product terms per output for logic functions. The sum of these products feeds the output macrocell. Each macrocell can be programmed as registered or combinatorial with an active high or active-low output after Break EPM3128ATC100 CPLD.

The output configuration is determined by two global bits and one local bit controlling four multiplexers in each macrocell.

AMD’s FusionPLD program allows PALCE16V8 designs to be implemented using a wide variety of popular industry-standard design tools. By working closely with the FusionPLD partners, AMD certifies that the tools provide accurate, quality support.

By ensuring that third party tools are available, costs are lowered because a designer does not have to buy a complete set of new tools for each device. The Fusion PLD program also greatly reduces design time since a designer can use a tool that is already installed and familiar.