Posts Tagged ‘break PIC18F4480 Microcontroller’

PIC18F4480 Microcontroller Memory Data Recovering

PIC18F4480 Microcontroller Memory Data Recovering

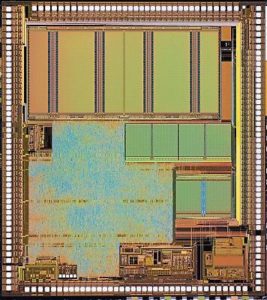

PIC18F4480 secured microcontroller memory data recovering can help engineer to extract embedded firmware of binary code or heximal file from locked microprocessor PIC18F4480 after crack MCU’s tamper resistance system and copy flash memory content with eeprom memory data

Il recupero sicuro dei dati della memoria del microcontroller PIC18F4480 può aiutare l’ingegnere a estrarre il firmware incorporato del codice binario o del file esimale dal microprocessore bloccato PIC18F4480 dopo il crack del sistema di resistenza alla manomissione dell’MCU e a copiare il contenuto della memoria flash con i dati della memoria eeprom

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible which can provide great benefit for PIC18F4480 Microcontroller Memory Data Recovering. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accom- plished with a RAM banking scheme.

PIC18F4480 Microcontroller Memory Data Recovering

This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18F4480 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 Most Significant bits of a location’s address; the instruction itself includes the 8 Least Significant bits.

Only the four lower bits of the BSR are implemented (BSR3:BSR0). The upper four bits are unused; they will always read ‘0’ and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

PIC18F4480 güvenli mikrodenetleyici bellek verilerinin kurtarılması, mühendisin, MCU’nun kurcalamaya karşı koruma sistemini kırdıktan ve eeprom bellek verileriyle flash bellek içeriğini kopyaladıktan sonra kilitli mikroişlemci PIC18F4480’den gömülü ikili kod veya onaltılık dosya yazılımını çıkarmasına yardımcı olabilir

The value of the BSR indicates the bank in data memory; the 8 bits in the instruction show the location in the bank and can be thought of as an offset from the bank’s lower boundary. The relationship between the BSR’s value and the bank division in data memory is shown in below Figure.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh will end up resetting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return ‘0’s. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 5-5 indicates which banks are implemented.

A PIC18F4480 védett mikrokontroller memóriaadatainak helyreállítása segíthet a mérnöknek a bináris kód vagy heximális fájl beágyazott firmware-jének kinyerésében a zárolt PIC18F4480 mikroprocesszorból az MCU szabotázsellenállási rendszerének feltörését követően, és a flash memória tartalmát az eeprom memóriaadatokkal másolhatja.