Posts Tagged ‘break ic source hex’

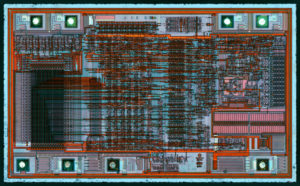

Break IC ATtiny85V Software

Break IC ATtiny85V Software

Break IC ATtiny85V can help engineer to readout the embedded firmware from mcu attiny85v flash and eeprom memory, fuse bit of microcontroller attiny85v can be cracked;

Break IC ATtiny85V can help engineer to readout the embedded firmware from mcu attiny85v flash and eeprom memory, fuse bit of microcontroller attiny85v can be cracked

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-IC oscillator, as shown in Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

In idle mode, the CPU puts itself to sleep while all the on-IC peripherals remain active. The mode is invoked by software. The content of the on-IC RAM and all the special functions registers remain unchanged during Break mcu pic16f876 memory.

Figure 2. External Clock Drive Configuration mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset before Break IC. It should be noted that when idle is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-IC hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited.

To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory. In the power down mode the oscillator is stopped, and the instruction that invokes power down is the last instruction executed. The on-IC RAM and Special Function Registers retain their values until the power down mode is terminated.

The only exit from power down is a hardware reset. Reset redefines the SFRs but does not change the on-IC RAM. The reset should not be activated before VCC is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize if Break IC.

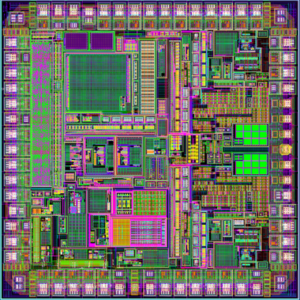

Break IC ATtiny45 Heximal

Break IC ATtiny45 Heximal

Break IC ATtiny45 and readout Heximal from mcu attiny45 flash memory, unlock microcontroller attiny45 security fuse bit and remove the protection;

Port B is a 6-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated.

The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running. Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running.

The minimum pulse length is given in Table 23-3 on page 170. Shorter pulses are not guaranteed to generate a reset. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written. I/O Registers within the address range 0x00 – 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions when Break pic16f616 IC.

Some of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operation the specified bit, and can therefore be used on registers containing such Status Flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

The ATTINY45 provides the following standard features:

20K bytes of Flash, 256-bytes of RAM, 32 I/O lines, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89C55 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes.

The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power Down Mode saves the RAM contents but freezes the oscillator, disabling all other chip functions until the next hardware reset. The low-voltage option saves power and operates with a 2.7-volt power supply if Break IC.