Posts Tagged ‘break attiny88 mcu’

Break IC ATtiny88 Heximal

Break IC ATtiny88 Heximal

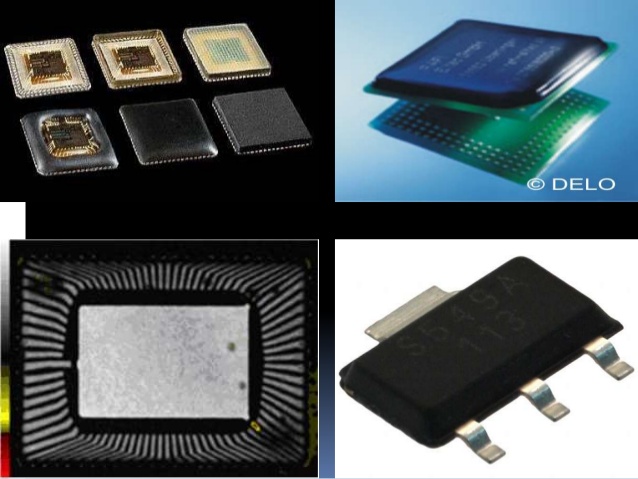

Break IC ATtiny88 flash and eeprom memory, then readout Heximal from MCU ATtiny88 program memory, unlock microcontroller attiny88 security fuse bit and extract the embedded firmware;

High Performance, Low Power AVR® 8-Bit Microcontroller

Advanced RISC Architecture

– 123 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation if reverse engineering microcontroller pic16c558a

High Endurance Non-volatile Memory Segments

– 4K/8K Bytes of In-System Self-Programmable Flash program memory(ATtiny48/88)

– 64/64 Bytes EEPROM (ATtiny48/88)

– 256/512 Bytes Internal SRAM (ATtiny48/88)

– Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85°C / 100 years at 25°C

– Programming Lock for Software Security

Peripheral Features

– One 8-bit Timer/Counter with Separate Prescaler and Compare Mode

– One 16-bit Timer/Counter with Prescaler, and Compare and Capture Modes

– 8-channel 10-bit ADC in 32-lead TQFP and 32-pad QFN/MLF package

– 6-channel 10-bit ADC in 28-pin PDIP and 28-pad QFN/MLF package

– Master/Slave SPI Serial Interface

– Byte-oriented 2-wire Serial Interface (Philips I2C Compatible)

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

– Interrupt and Wake-up on Pin Change

Special Microcontroller Features

– debugWIRE On-chip Debug System

– In-System Programmable via SPI Port

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated Oscillator before Break mcu pic12f519 binary

– External and Internal Interrupt Sources

– Three Sleep Modes: Idle, ADC Noise Reduction and Power-down I/O and Packages

– 28 Programmable I/O Lines in 32-lead TQFP and 32-pad QFN/MLF package

– 24 Programmable I/O Lines in 28-pin PDIP and 28-pad QFN/MLF package

– 28-pin PDIP, 32-lead TQFP, 28-pad QFN/MLF and 32-pad QFN/MLF

Operating Voltage:

– 1.8 – 5.5V

Temperature Range:

– -40°C to +85°C

Speed Grade:

– 0 – 4 MHz @ 1.8 – 5.5V

– 0 – 8 MHz @ 2.7 – 5.5V

– 0 – 12 MHz @ 4.5 – 5.5V

– Active Mode: 1 MHz, 1.8V: 240µA

– Power-down Mode: 0.1µA at 1.8V

Port A is a 4-bit bi-directional I/O port with internal pull-up resistors (selected for each bit) in 32-lead TQFP and 32-pad QFN/MLF package. The PA3..0 output buffers have symmetrical drive characteristics with both high sink and source capability.

As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tristated when a reset condition becomes active, even if the clock is not running.