Posts Tagged ‘папраўляцца Intergated замыкання file’

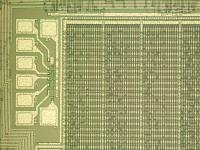

Copy Chip PIC18F252 Flash

Copy Chip PIC18F252 Flash

We can Copy Chip PIC18F252 Flash, please view below Chip PIC18F252 features for your reference:

Power Management Features:

Run: CPU on, Peripherals on

Idle: CPU off, Peripherals on

Sleep: CPU off, Peripherals off

Ultra Low 50nA Input Leakage

Run mode Currents Down to 11 ìA Typical

Idle mode Currents Down to 2.5 ìA Typical

Sleep mode Current Down to 100 nA Typical

Timer1 Oscillator: 900 nA, 32 kHz, 2V

Watchdog Timer: 1.4 ìA, 2V Typical

Two-Speed Oscillator Start-up

· Master Synchronous Serial Port (MSSP) module

Master and Slave modes

· Enhanced Addressable USART module:

– Supports RS-485, RS-232 and LIN/J2602

– RS-232 operation using internal oscillator

block (no external crystal required)

– Auto-wake-up on Start bit

– Auto-Baud Detect

· 10-Bit, up to 13-Channel Analog-to-Digital (A/D)

Flexible Oscillator Structure:

· Four Crystal modes, up to 40 MHz

· 4x Phase Lock Loop (PLL) – Available for Crystal

and Internal Oscillators

· Two External RC modes, up to 4 MHz

· Two External Clock modes, up to 40 MHz

· Internal Oscillator Block:

– Fast wake from Sleep and Idle, 1 ìs typical

– 8 use-selectable frequencies, from 31 kHz to 8 MHz

– Provides a complete range of clock speeds

from 31 kHz to 32 MHz when used with PLL

– User-tunable to compensate for frequency drift

· Secondary Oscillator using Timer1 @ 32 kHz

· Fail-Safe Clock Monitor:

– Allows for safe shutdown if peripheral clock stops

Peripheral Highlights:

Converter module:

– Auto-acquisition capability

– Conversion available during Sleep

· Dual Analog Comparators with Input Multiplexing

· Programmable 16-Level High/Low-Voltage

Detection (HLVD) module:

– Supports interrupt on High/Low-Voltage Detection

Special Microcontroller Features:

· C Compiler Optimized Architecture:

– Optional extended instruction set designed to optimize re-entrant code

· 100,000 Erase/Write Cycle Enhanced Flash

Program Memory Typical

· 1,000,000 Erase/Write Cycle Data EEPROM

Memory Typical

· Flash/Data EEPROM Retention: 100 Years Typical which is important for IC Extraction

· Self-Programmable under Software Control

High-Current Sink/Source 25 mA/25 mA

Three Programmable External Interrupts

Four Input Change Interrupts

Up to 2 Capture/Compare/PWM (CCP) modules,

· Priority Levels for Interrupts

· 8 x 8 Single-Cycle Hardware Multiplier

· Extended Watchdog Timer (WDT):

– Programmable period from 4 ms to 131s

one with Auto-Shutdown (28-pin devices)

· Enhanced Capture/Compare/PWM (ECCP)

module (40/44-pin devices only):

– One, two or four PWM outputs

– Selectable polarity

– Programmable dead time

– Auto-shutdown and auto-restart

· Single-Supply 5V In-Circuit Serial

Programming™ (ICSP™) via Two Pins

· In-Circuit Debug (ICD) via Two Pins

· Wide Operating Voltage Range: 2.0V to 5.5V

· Programmable Brown-out Reset (BOR) with

Software Enable Option