Posts Tagged ‘атаковать интегральная схема firmware’

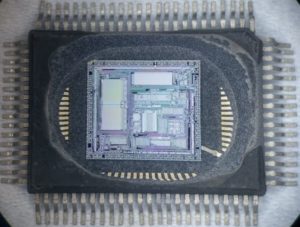

Copy CPLD EPM9320ARC208-10 Binary

Copy CPLD EPM9320ARC208-10 Binary

High-performance CMOS EEPROM-based programmable logic devices (PLDs) built on third-generation Multiple Array MatriX (MAX®) architecture which is the main reason for requirement on Copy CPLD EPM9320ARC208-10 Binary.

Copy CPLD EPM9320ARC208-10 Binary

5.0-V in-system programmability (ISP) through built-in IEEE Std.

1149.1 Joint Test Action Group (JTAG) interface

Built-in JTAG boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990

High-density erasable programmable logic device (EPLD) family ranging from 6,000 to 12,000 usable gates (see Table 1)

10-ns pin-to-pin logic delays with counter frequencies of up to 144 MHz

Fully compliant with the peripheral component interconnect Special Interest Group’s (PCI SIG) PCI Local Bus Specification, Revision 2.2

Dual-output macrocell for independent use of combinatorial and registered logic

FastTrack® Interconnect for fast, predictable interconnect delays

Input/output registers with clear and clock enable on all I/O pins

Programmable output slew-rate control to reduce switching noise

MultiVolt™ I/O interface operation, allowing devices to interface with 3.3-V and 5.0-V devices

Configurable expander product-term distribution allowing up to 32 product terms per macrocell

Programmable power-saving mode for more than 50% power reduction in each macrocell

Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

Programmable security bit for protection of proprietary designs which must be disable when Copy CPLD EPM9320ARC208-10 Binary

Software design support and automatic place-and-route

Altera’s MAX+PLUS® II development system on Windows-based PCs as well as Sun SPARCstation, HP 9000 Series 700/800, and IBM RISC System/6000 workstations

Additional design entry and simulation support provided by EDIF 200 and 300 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest

Programming support with Altera’s Master Programming Unit (MPU), BitBlasterTM serial download cable, ByteBlasterTM parallel port download cable, and ByteBlasterMVTM parallel port download cable, as well as programming hardware from third-party manufacturers.

Offered in a variety of package options with 84 to 356 pins.