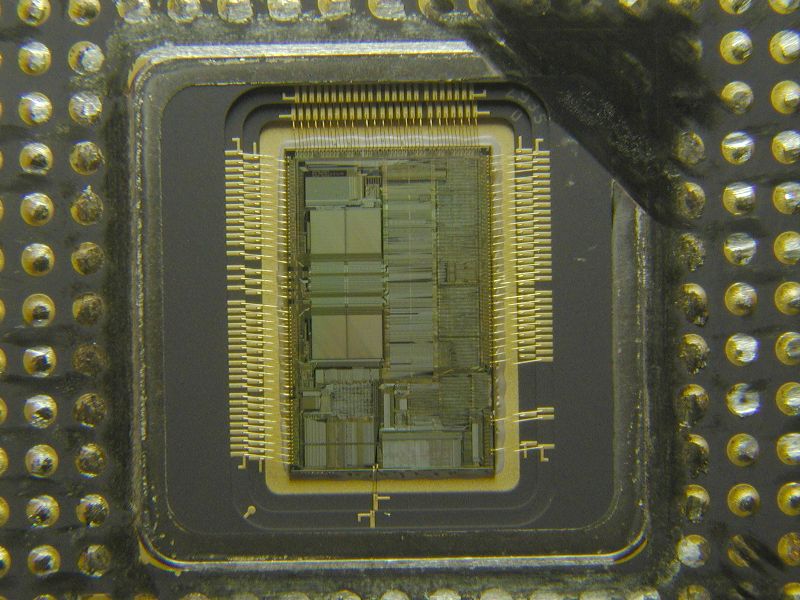

Reverse Engineering PIC18F65K22 Microchip MCU Flash Memory

Reverse Engineering PIC18F65K22 Microchip MCU Flash Memory

Reverse Engineering PIC18F65K22 Microchip MCU Flash Memory needs to unlock mcu pic18f65k22 security fuse bit and extract embedded heximal from its memory;

For more information about the modes discussed in this section see Section 3.0 “Power-Managed Modes”. A quick reference list is also available in Table 3-1.

When PRI_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC_RUN and SEC_IDLE), the secondary oscillator (SOSC) is operating and providing the device clock to facilitate the process of attacking microchip mcu pic18f46k80 memory. The secondary oscillator may also run in all power- managed modes if required to clock Timer1, Timer3 or Timer5.

In internal oscillator modes (INTOSC_RUN and INTOSC_IDLE), the internal oscillator block provides the device clock source. The 31.25 kHz LFINTOSC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode