Restore R5F211A2SP IC MCU Flash Memory Data

Restore R5F211A2SP IC MCU Flash Memory Data

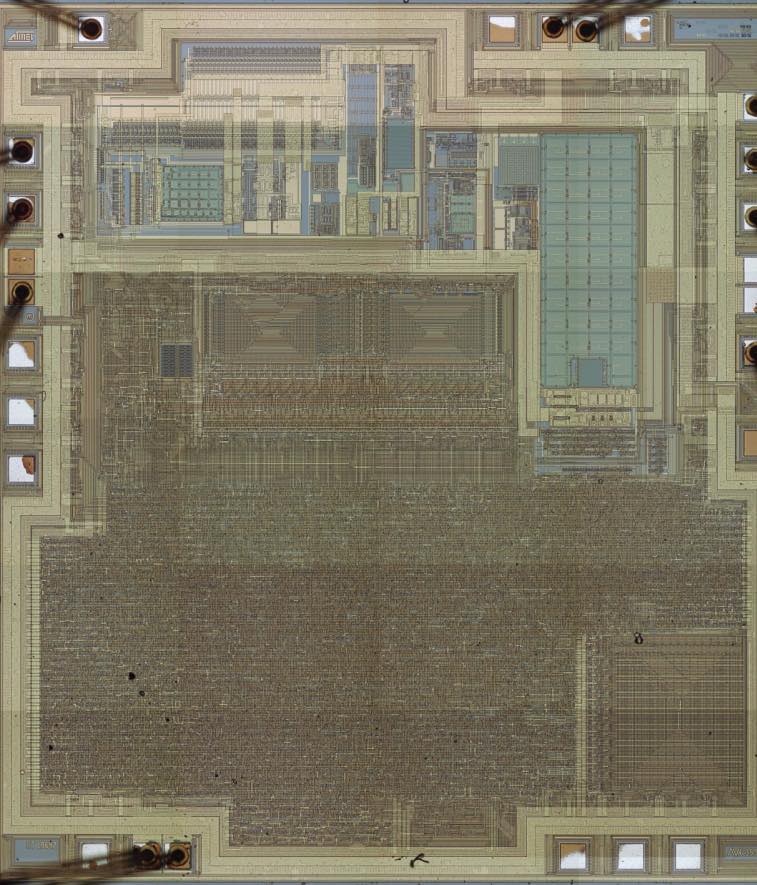

Restore R5F211A2SP IC MCU Flash Memory Data needs to reverse engineering microcontroller r5f211a2sp locked fuse bit, readout embedded binary file from microprocessor r5f211a2sp flash memory;

The R8C/33A Group of single-chip MCUs incorporates the R8C/Tiny Series CPU core, employing sophisticated instructions for a high level of efficiency. With 1 Mbyte of address space to recover microcontroller r5f21324cnsp flash program, and it is capable of executing instructions at high speed. In addition, the CPU core boasts a multiplier for high-speed operation processing.

Power consumption is low, and the supported operating modes allow additional power control. These MCUs also use an anti-noise configuration to reduce emissions of electromagnetic noise and are designed to withstand EMI.

restaurar R5F211A2SP IC MCU dados de memória flash precisa de engenharia reversa microcontrolador r5f211a2sp bloqueado bit fusível, leitura de arquivo binário incorporado do microprocessador r5f211a2sp memória flash

Integration of many peripheral functions, including multifunction timer and serial interface, reduces the number of system components to break r5f21336tn mcu flash. The R8C/33A Group has data flash (1 KB × 4 blocks) with the background operation (BGO) function.

R8C/Tiny series core

- Number of fundamental instructions: 89

- Minimum instruction execution time:

50 ns (f(XIN) = 20 MHz, VCC = 3.0 to 5.5 V)

100 ns (f(XIN) = 10 MHz, VCC = 2.7 to 5.5 V)

200 ns (f(XIN) = 5 MHz, VCC = 2.2 to 5.5 V)

500 ns (f(XIN) = 2 MHz, VCC = 1.8 to 5.5 V)

- Multiplier: 16 bits × 16 bits ® 32 bits

- Multiply-accumulate instruction: 16 bits × 16 bits + 32 bits ® 32 bits

Operation mode: Single-chip mode (address space: 1 Mbyte)