Recover Texas DSP Microcpu TMS320F280230 Locked Flash Firmware

Recover Texas DSP Microcpu TMS320F280230 Locked Flash Firmware

Recover Texas DSP Microcpu TMS320F280230 Locked Flash Firmware needs to crack protected cpu tms320f280230 memory and readout the embedded firmware from microcontroller;

All output signals from the 28x devices (including XCLKOUT) are derived from an internal clock such that all output transitions for a given half-cycle occur with a minimum of skewing relative to each other.

The signal combinations shown in the following timing diagrams may not necessarily represent actual cycles. For actual cycle examples, see the appropriate cycle description section of this document when reverse dsp cpu tms320f28050 flash memory;

відновити TEXAS INSTRUMENT DSP, захищений мікроконтролер TMS320F280230PTT, заблоковану флеш-програму програмного забезпечення, яка потребує зламу захищеної пам’яті мікропроцесора TMS320F280230PTT і зчитування вихідного коду двійкового файлу або шістнадцяткових даних із зашифрованого MCU за допомогою пристрою READ-PROTECTION;

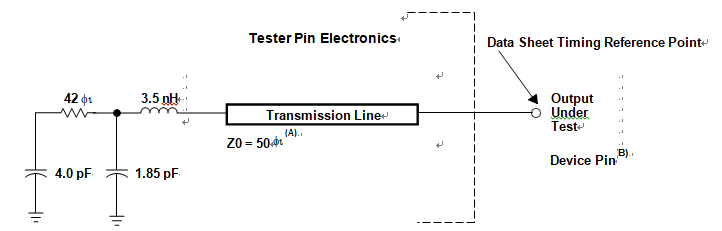

This test load circuit is used to measure all switching characteristics provided in this document.

A. Input requirements in this data sheet are tested with an input slew rate of < 4 Volts per nanosecond (4 V/ns) at the device pin.

B. The data sheet provides timing at the device pin. For output timing analysis, the tester pin electronics and its transmission line effects must be taken into account. A transmission line with a delay of 2 ns or longer can be used to produce the desired transmission line effect. The transmission line is intended as a load only.

recuperar el microcontrolador seguro TEXAS INSTRUMENT DSP TMS320F280230PTT programa de firmware flash bloqueado necesita descifrar la memoria TMS320F280230PTT del microprocesador protegido y leer el código fuente del archivo binario o datos heximales de la MCU cifrada con un dispositivo de PROTECCIÓN DE LECTURA;

It is not necessary to add or subtract the transmission line delay (2 ns or longer) from the data sheet timing.