Recover PIC MCU Microchip 16LF506 Firmware

Recover PIC MCU Microchip 16LF506 Firmware

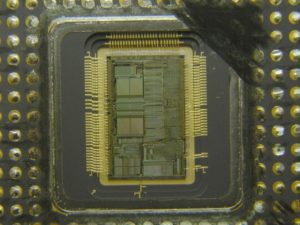

Recover PIC MCU Microchip 16LF506 Firmware and copy program to new Microcontroller PIC16LF506, clone master PIC16LF506 mcu which can provide the same functions as original master Microprocessor;

Recover PIC MCU Microchip 16LF506 Firmware and copy program to new Microcontroller PIC16LF506, clone master PIC16LF506 mcu which can provide the same functions as original master Microprocessor

Data memory is composed of registers or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers (SFR) and General Purpose Registers (GPR).

The Special Function Registers include the TMR0 register, the Program Counter (PCL), the STATUS register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Function Registers are used to control the I/O port configuration and prescaler options when Recover IC STM32F107RCT6 code.

The General Purpose Registers are used for data and control information under command of the instructions. For the PIC12F510, the register file is composed of 10 Special Function Registers, 6 General Purpose.

Registers and 32 General Purpose Registers accessed For the PIC16F506, the register file is composed of 13 Special Function Registers, 3 General Purpose Registers and 64 General Purpose Registers accessed.

unlock microcontroller PIC16F506 tamper resistance system and extract embedded program data from flash memory

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (see Table 4-1).

The Special Function Registers can be classified into two sets. The Special Function Registers associated with the “core” functions are described in this section for the purpose of chip AT89S8252 flash content copying.

Those related to the operation of the peripheral features are described in the section for each peripheral feature.

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register

as 000u u1uu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits.