Recover Microcontroller ATtiny13A Heximal

Recover Microcontroller ATtiny13A Heximal

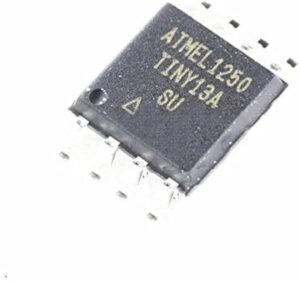

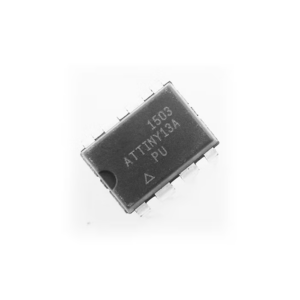

Recovering microcontroller ATtiny13A heximal involves a process of cracking or decoding the secured firmware stored in its flash memory and EEPROM memory of encrypted MCU ATtiny13A. The ATtiny13A, like many microcontrollers (MCUs), may have encrypted or locked firmware to protect its program and source code. However, using reverse engineering techniques, experts can break these ATtiny13A microprocessor’s protective layers and unlock the microprocessor’s memory to retrieve the heximal data.

Recovering microcontroller ATtiny13A heximal involves a process of cracking or decoding the secured firmware stored in its flash memory and EEPROM memory of encrypted MCU ATtiny13A. The ATtiny13A, like many microcontrollers (MCUs), may have encrypted or locked firmware to protect its program and source code. However, using reverse engineering techniques, experts can break these ATtiny13A microprocessor’s protective layers and unlock the microprocessor’s memory to retrieve the heximal data.

The recovery process starts by analyzing the microcontroller’s architecture to identify encryption protocols. Once these protections are bypassed, the binary or heximal firmware can be extracted. This data is essential for restoring or replicating the original program, enabling system recovery or hardware duplication.

Decoding or decrypting the ATtiny13A’s firmware allows developers to restore lost data or replicate the software for new devices. However, these actions must be conducted within legal and ethical guidelines to avoid violating intellectual property rights.

The AVR core combines a rich instruction set with 32 general purpose working registers which will provide benefit for Recover Microcontroller ATtiny13A Heximal. All 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATtiny13A provides the following features: 1K byte of In-System Programmable Flash, 64 bytes EEPROM, 64 bytes SRAM, 6 general purpose I/O lines, 32 general purpose working registers, one 8-bit Timer/Counter with compare modes, Internal and External Interrupts, a 4-channel, 10-bit ADC, a programmable Watchdog Timer with internal Oscillator, and three software selectable power saving modes if Recover Microcontroller ATTINY13A Heximal.

mbalekake microcontroller ATtiny13A heximal melu proses cracking utawa dekoding perangkat kukuh aman disimpen ing memori lampu kilat lan memori EEPROM saka ndhelik MCU ATtiny13A. ATtiny13A, kaya akeh mikrokontroler (MCU), bisa uga duwe perangkat kukuh sing dienkripsi utawa dikunci kanggo nglindhungi program lan kode sumber. Nanging, kanthi nggunakake teknik rekayasa terbalik, para ahli bisa ngilangi lapisan pelindung mikroprosesor ATtiny13A iki lan mbukak kunci memori mikroprosesor kanggo njupuk data heksimal.

The Idle mode stops the CPU while allowing the SRAM, Timer/Counter, ADC, Analog Comparator, and Interrupt system to continue functioning. The Power-down mode saves the register contents, disabling all chip functions until the next Interrupt or Hardware Reset. The ADC Noise Reduction mode stops the CPU and all I/O modules except ADC, to minimize switching noise during ADC conversions.

The device is manufactured using Atmel’s high density non-volatile memory technology. The On-chip ISP Flash allows the Program memory to be re-programmed In-System through an SPI serial interface, by a conventional non-volatile memory programmer or by an On-chip boot code running on the AVR core.

The ATtiny13A AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, and Evaluation kits if Recover MICROCONTROLLER.

మైక్రోకంట్రోలర్ ATtiny13A హెక్సిమల్ని పునరుద్ధరించడం అనేది దాని ఫ్లాష్ మెమరీలో నిల్వ చేయబడిన సురక్షిత ఫర్మ్వేర్ మరియు ఎన్క్రిప్టెడ్ MCU ATtiny13A యొక్క EEPROM మెమరీని క్రాకింగ్ లేదా డీకోడింగ్ చేసే ప్రక్రియను కలిగి ఉంటుంది. ATtiny13A, అనేక మైక్రోకంట్రోలర్ల (MCUలు) వలె, దాని ప్రోగ్రామ్ మరియు సోర్స్ కోడ్ను రక్షించడానికి ఫర్మ్వేర్ను ఎన్క్రిప్ట్ చేసి లేదా లాక్ చేసి ఉండవచ్చు. అయినప్పటికీ, రివర్స్ ఇంజనీరింగ్ పద్ధతులను ఉపయోగించి, నిపుణులు ఈ ATtiny13A మైక్రోప్రాసెసర్ యొక్క రక్షణ పొరలను విచ్ఛిన్నం చేయవచ్చు మరియు హెక్సిమల్ డేటాను తిరిగి పొందడానికి మైక్రోప్రాసెసర్ మెమరీని అన్లాక్ చేయవచ్చు.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written when Break IC PIC16F684 Binary.

I/O Registers within the address range 0x00 – 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.ome of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operation the specified bit, and can therefore be used on registers containing such Status Flags. The CBI and SBI instructions work with registers 0x00 to 0x1F.

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

Die Wiederherstellung des Mikrocontrollers ATtiny13A Heximal umfasst einen Prozess zum Knacken oder Dekodieren der gesicherten Firmware, die im Flash-Speicher und EEPROM-Speicher des verschlüsselten MCU ATtiny13A gespeichert ist. Der ATtiny13A kann, wie viele Mikrocontroller (MCUs), eine verschlüsselte oder gesperrte Firmware haben, um sein Programm und seinen Quellcode zu schützen. Mithilfe von Reverse-Engineering-Techniken können Experten jedoch diese Schutzschichten des ATtiny13A-Mikroprozessors durchbrechen und den Speicher des Mikroprozessors entsperren, um die Heximal-Daten abzurufen.