Recover IC STM32F107RCT6 Code

Recover IC STM32F107RCT6 Code

The STM32F107RCT6 is a high-performance ARM Cortex-M3 based microcontroller by STMicroelectronics, widely used in industrial, automotive, and embedded systems due to its integrated Ethernet MAC, USB OTG, CAN, and rich peripheral features. However, many applications implement protective measures to prevent firmware extraction, making it extremely difficult to readout, copy, or clone the original program. At [Your Company Name], we offer professional services to recover IC STM32F107RCT6 code, helping clients unlock, decrypt, and replicate protected firmware, even from locked or secured memory blocks.

STM32F107RCT6 — это высокопроизводительный микроконтроллер на базе ARM Cortex-M3 от STMicroelectronics, широко используемый в промышленных, автомобильных и встраиваемых системах благодаря интегрированным Ethernet MAC, USB OTG, CAN и богатым периферийным функциям. Однако во многих приложениях реализованы защитные меры для предотвращения извлечения прошивки, что делает чрезвычайно сложным считывание, копирование или клонирование исходной программы. В Circuit Engineering Co.,LTD мы предлагаем профессиональные услуги по восстановлению кода IC STM32F107RCT6, помогая клиентам разблокировать, расшифровать и скопировать защищенную прошивку даже из заблокированных или защищенных блоков памяти.

Why Recover STM32F107RCT6 Firmware?

There are many valid reasons to recover embedded firmware from STM32 microcontrollers:

-

Legacy Support: Recovering firmware, binary, or heximal files from legacy systems where source code is lost.

-

System Migration: Transferring a protected program to a newer hardware platform.

-

Security Research: Analyzing secured firmware archives for vulnerabilities.

-

Product Cloning & Duplication: Replicating locked source code for batch production or testing.

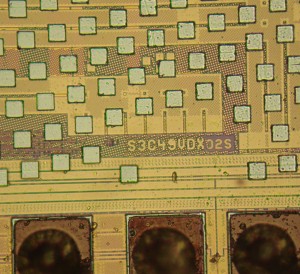

Recover IC STM32F107RCT6 code from MCU STM32F107RCT6 program memory, use MCU cracking technique to remove the security fuse by focus ion beam

Recover IC STM32F107RCT6 code from MCU STM32F107RCT6 program memory, use MCU cracking technique to remove the security fuse by focus ion beam;

Core: ARM 32-bit Cortex™-M3 CPU

– 72 MHz maximum frequency, 1.25 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state memory

LQFP100 14 × 14 mm

LQFP64 10 × 10 mm

LFBGA100 10 × 10 mm

– Single-cycle multiplication and hardware division

Memories

– 64 to 256 Kbytes of Flash memory

– 64 Kbytes of general-purpose SRAM Clock, reset and supply management

– 2.0 to 3.6 V application supply and I/Os

– POR, PDR, and programmable voltage detector (PVD)

– 3-to-25 MHz crystal oscillator

– Internal 8 MHz factory-trimmed RC

– Internal 40 kHz RC with calibration

– 32 kHz oscillator for RTC with calibration

STM32F107RCT6는 STMicroelectronics의 고성능 ARM Cortex-M3 기반 마이크로컨트롤러로, 이더넷 MAC, USB OTG, CAN 및 풍부한 주변 장치 기능을 통합하여 산업, 자동차 및 임베디드 시스템에서 널리 사용됩니다. 그러나 많은 애플리케이션에서 펌웨어 추출을 방지하기 위한 보호 기능이 구현되어 있어 원본 프로그램을 읽거나 복사하거나 복제하는 것이 매우 어렵습니다. Circuit Engineering Co.,LTD는 IC STM32F107RCT6 코드 복구 전문 서비스를 제공하여 고객이 잠기거나 보안된 메모리 블록에서도 보호된 펌웨어를 잠금 해제, 복호화 및 복제할 수 있도록 지원합니다.

Low power

– Sleep, Stop and Standby modes

– VBAT supply for RTC and backup registers 2 × 12-bit, 1 µs A/D converters (16 channels)

– Conversion range: 0 to 3.6 V

– Sample and hold capability

– Temperature sensor

– up to 2 MSPS in interleaved mode 2 × 12-bit D/A converters DMA: 12-channel DMA controller

– Supported peripherals: timers, ADCs, DAC, I2Ss, SPIs, I2Cs and USARTs

Up to 10 timers with pinout remap capability

– Up to four 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

– 1 × 16-bit motor control PWM timer with dead-time generation and emergency stop

– 2 × watchdog timers (Independent and Window)

– SysTick timer: a 24-bit downcounter

– 2 × 16-bit basic timers to drive the DAC Up to 14 communication interfaces with pinout remap capability

– Up to 2 × I2C interfaces (SMBus/PMBus)

STM32F107RCT6, entegre Ethernet MAC, USB OTG, CAN ve zengin çevre birimi özellikleri sayesinde endüstriyel, otomotiv ve gömülü sistemlerde yaygın olarak kullanılan STMicroelectronics tarafından üretilen yüksek performanslı bir ARM Cortex-M3 tabanlı mikrodenetleyicidir. Ancak birçok uygulama, ürün yazılımının çıkarılmasını önlemek için koruyucu önlemler uygular ve bu da orijinal programı okumayı, kopyalamayı veya klonlamayı son derece zorlaştırır. Circuit Engineering Co.,LTD’de, IC STM32F107RCT6 kodunu kurtarmak için profesyonel hizmetler sunuyoruz ve müşterilerin kilitli veya güvenli bellek bloklarından bile korumalı ürün yazılımını kilidini açmalarına, şifresini çözmelerine ve çoğaltmalarına yardımcı oluyoruz.

– Up to 5 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)

– Up to 3 SPIs (18 Mbit/s), 2 with a multiplexed I2S interface that offers audio class accuracy via advanced PLL schemes

– 2 × CAN interfaces (2.0B Active) with 512 bytes of dedicated SRAM

– USB 2.0 full-speed device/host/OTG controller with on-chip PHY that supports

HNP/SRP/ID with 1.25 Kbytes of dedicated SRAM

– 10/100 Ethernet MAC with dedicated DMA and SRAM (4 Kbytes): IEEE1588 hardware support, MII/RMII available on all packages

– Cortex-M3 Embedded Trace Macrocell™ Up to 80 fast I/O ports

– 51/80 I/Os, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant CRC calculation unit, 96-bit unique ID