Reverse Engineering Microchip PIC16F1913 Memory

Reverse Engineering Microchip PIC16F1913 Memory

Reverse Engineering Microchip PIC16F1913 Memory

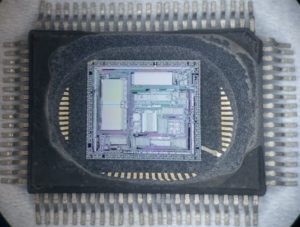

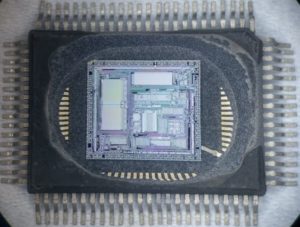

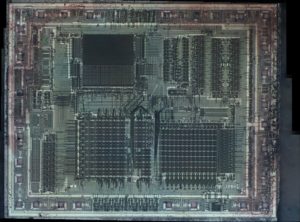

Reverse Engineering Microchip PIC16F1913 Memory means delayer the silicon, plastic and metal layer from PIC16F1913 and counter sequence of microcontroller manufacturing:

High-Performance RISC CPU:

· Only 35 instructions to learn:

– All single-cycle instructions except branches

· Operating speed:

– DC – 20 MHz oscillator/clock input

– DC – 200 ns instruction cycle

· Program Memory Read (PMR) capability

· Interrupt capability

· 8-level deep hardware stack

· Direct, Indirect and Relative Addressing modes

Special Microcontroller Features:

· Precision Internal Oscillator:

– Factory calibrated to ±1%, typical

– Software selectable frequency range of

8 MHz to 125 kHz

– Software tunable

– Two-Speed Start-up mode

– External Oscillator fail detect for critical applications

– Clock mode switching during operation for power savings

· Software selectable 31 kHz internal oscillator

· Power-Saving Sleep mode

· Wide operating voltage range (2.0V-5.5V)

· Industrial and Extended temperature range

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up

Timer (OST)

· Brown-out Reset (BOR) with software control option

· Enhanced Low-Current Watchdog Timer (WDT) with on-chip oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

· Multiplexed Master Clear with pull-up/input pin

· Programmable code protection

· High-Endurance Flash/EEPROM cell:

– 100,000 write Flash endurance

– 1,000,000 write EEPROM endurance

– Flash/Data EEPROM retention: > 40 years

Low-Power Features:

· Standby Current:

– <100 nA @ 2.0V, typical

· Operating Current:

– 11 ìA @ 32 kHz, 2.0V, typical

– 220 ìA @ 4 MHz, 2.0V, typical

· Watchdog Timer Current:

– 1 ìA @ 2.0V, typical

Peripheral Features:

· Liquid Crystal Display module:

– Up to 60/96/168 pixel drive capability on 28/40/64-pin devices, respectively

– Four commons

· Up to 24/35/53 I/O pins and 1 input-only pin:

– High-current source/sink for direct LED drive

– Interrupt-on-change pin

– Individually programmable weak pull-ups

· In-Circuit Serial Programming™ (ICSP™) via two pins if Reverse Engineering Microchip PIC16F1913 Memory

· Analog comparator module with:

– Two analog comparators

– Programmable on-chip voltage reference (CVREF) module (% of VDD)

– Comparator inputs and outputs externally accessible

· A/D Converter:

– 10-bit resolution and up to 8 channels

· Timer0: 8-bit timer/counter with 8-bit programmable prescaler

· Enhanced Timer1:

– 16-bit timer/counter with prescaler

– External Timer1 Gate (count enable)

– Option to use OSC1 and OSC2 as Timer1 oscillator if INTOSCIO or LP mode is selected

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Addressable Universal Synchronous

Asynchronous Receiver Transmitter (AUSART)

· Up to 2 Capture, Compare, PWM modules:

– 16-bit Capture, max. resolution 12.5 ns

– 16-bit Compare, max. resolution 200 ns

– 10-bit PWM, max. frequency 20 kHz

· Synchronous Serial Port (SSP) with I2C™

Extract Lattice CPLD Source Code

Extract Lattice CPLD Source Code

Extract Lattice CPLD Source Code from embedded memory needs to reset the status of CPLD chip from locked to open one by CPLD chip unlocking technique, the content inside the CPLD memory can be readout directly with universal programmer;

Extract Lattice CPLD Source Code from embedded memory needs to reset the status of CPLD chip from locked to open one by CPLD chip unlocking technique, the content inside the CPLD memory can be readout directly with universal programmer

A slightly different approach is required for reverse engineering CPLDs and FPGAs. Even if the security protection is defeated and the attacker manages to extract the configuration bitstream file from the device, he will have to spend a substantial amount of time and effort to convert it into the logic equations and primitive blocks for further simulation and analysis. Meantime, there are some companies on the market, for example Bottom Line Technologies [111], which provide bitstream reverse engineering for CPLDs and FPGAs.

Extract DSP CPLD Encrypted Software

Extract DSP CPLD Encrypted Software

Extract DSP CPLD Encrypted Software from memory start from disable the tamper resistance, by using MCU invasive cracking will help to disclose the internal structure of CPLD chip;

Extract DSP CPLD Encrypted Software from memory start from disable the tamper resistance, by using MCU invasive cracking will help to disclose the internal structure of CPLD chip

When it comes to reverse engineering smartcards and microcontrollers, both structural and program-code reverse engineering are required to understand how the device works. First, the security protection needs to be understood by partial reverse engineering of the chip area associated with it. Thus if memory bus encryption was used, the hardware responsible for this should be reverse engineered. Then, finally, the internal memory contents have to be extracted and disassembled to understand device functions.

Crack Lattice CPLD Embeded Firmware

Crack Lattice CPLD Embeded Firmware

Crack Lattice CPLD Embeded Firmware from its memory, copy jed content to blank Lattice CPLD which will provide the same functions as original master CPLD, this microcontroller security unlocking technique can help engineer to extract jed file from master CPLD.

Crack Lattice CPLD Embeded Firmware from its memory, copy jed content to blank Lattice CPLD which will provide the same functions as original master CPLD.

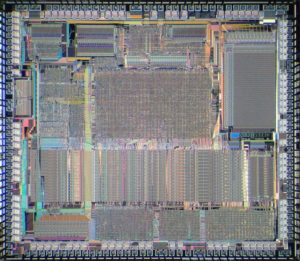

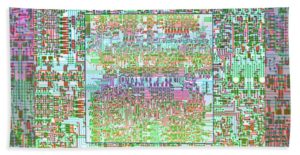

Reverse engineering is a technique aimed at understanding the structure of a semiconductor device and its functions. In case of an ASIC or a custom IC, that means extracting information about the location of all the transistors and interconnections. In order to succeed, a general knowledge of IC and VLSI design is required.

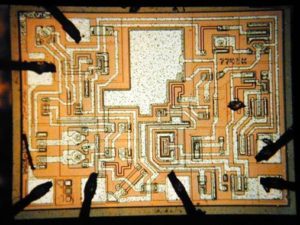

All the layers formed during chip fabrication are removed one-by-one in reverse order and photographed to determine the internal structure of the chip. In the end, by processing all the acquired information, a standard netlist file can be created and used to simulate the device. This is a tedious and time-consuming process, but there are some companies, for example Chipworks [110], which do such work as a standard service.

Crack DSP CPLD IC Chip File

Crack DSP CPLD IC Chip File

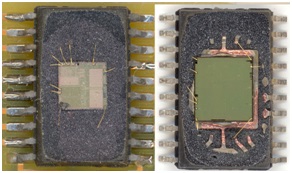

Crack DSP CPLD IC Chip Memory and extract file from DSP Chip flash memory, DSP IC cracking process normally start from decapsulate the silicon package of CPLD chip;

Crack DSP CPLD IC Chip Memory and extract file from DSP Chip flash memory, DSP IC cracking process normally start from decapsulate the silicon package of CPLD chip

For wet chemical etching we used the Nitrox wet etchant – one of the most effective etching agents for silicon nitride and silicon dioxide passivation layers which selectively removes the passivation layers of integrated circuits while preserving full device functionality.

To observe deeper layers, top aluminium layers were etched away with a 20% water solution of hydrochloric acid HCl or 33% water solution of potassium hydroxide KOH. Although wet etching does not provide good uniformity across the die surface, a lot of information about the internal chip structure can be obtained. Examples of such operations are presented

As can be seen, wet chemical etching does not provide very good uniformity over the surface resulting in some areas where the top metal is not entirely removed and other areas where the underneath layer is starting to be etched. Also, as can be seen in Figure 57, some long metal wires lifted off the surface obstructing the view.

Deprocessing using wet chemical etching does not require much more experience than decapsulation and all the necessary chemicals can be bought for about £100. Care must be taken during the work, as these chemicals are very aggressive and dangerous, especially the ones containing fluorine.

Crack Microcontroller IC Source Code

Crack Microcontroller IC Source Code

Crack Microcontroller IC can help engineer to readout Source Code from MCU flash memory and eeprom memory, focus ion beam technique will be applied to remove the tamper resistance system of Microprocessor for Unlocking;

Crack Microcontroller IC can help engineer to readout Source Code from MCU flash memory and eeprom memory, focus ion beam technique will be applied to remove the tamper resistance system of Microprocessor for Unlocking

For wet and dry etching, each type of material requires certain etchants to be used. Some of them have very high selectivity and remove only the desired layer; others affect many layers at a time. For example, silicon and polysilicon can be etched with a mixture of hydrofluoric acid HF and nitric acid HNO3, but HF etches silicon oxide as well.

Other etchants are used for specific purposes, such as doping etchants with a doping-dependent etch rate to make visible doping fronts and p-n junctions. Such etchants are used, for example, to make visible the contents of VTROM in modern smartcards [8]. More information about different etchants and etching technology can be found in the literature on failure analysis techniques.

Reverse Engineering ATmel Chip Atmega8L-8PU

Reverse Engineering ATmel Chip Atmega8L-8PU

Reverse engineering ATmel Chip Atmega8L-8PU

Reverse engineering ATmel Chip Atmega8L-8PU means the content from both its eeprom and flash can be extracted and download it to other blank ATmega8L which will provide the same functions:

High-performance, Low-power AVR 8-bit Microcontroller

· Advanced RISC Architecture

– 130 Powerful Instructions – Most Single-clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-chip 2-cycle Multiplier

High Endurance Non-volatile Memory segments

– 8K Bytes of In-System Self-programmable Flash program memory

– 512 Bytes EEPROM

– 1K Byte Internal SRAM

– Write/Erase Cycles: 10,000 Flash/100,000 EEPROM (1)(3)

– Data retention: 20 years at 85°C/100 years at 25°C (2)(3)

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program True Read-While-Write Operation

– Programming Lock for Software Security

Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescaler, one Compare Mode

– One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

– Real Time Counter with Separate Oscillator

– Three PWM Channels

– 8-channel ADC in TQFP and QFN/MLF package

Eight Channels 10-bit Accuracy

– 6-channel ADC in PDIP package

Six Channels 10-bit Accuracy

– Byte-oriented Two-wire Serial Interface

– Programmable Serial USART

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Five Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, and Standby I/O and Packages

– 23 Programmable I/O Lines from Reverse engineering ATmel Chip Atmega8L-8PU

– 28-lead PDIP, 32-lead TQFP, and 32-pad QFN/MLF Operating Voltages

– 2.7 – 5.5V (ATmega8L)

– 4.5 – 5.5V (ATmega8) Speed Grades

– 0 – 8 MHz (ATmega8L)

– 0 – 16 MHz (ATmega8)

Power Consumption at 4 Mhz, 3V, 25°C

– Active: 3.6 mA

– Idle Mode: 1.0 mA

– Power-down Mode: 0.5 µA

Recover TI MSP430G2452 Embedded Memory

Recover TI MSP430G2452 Embedded Memory

Recover TI MSP430G2452 Embedded Memory

Recover TI MSP430G2452 Embedded Memory starts from acquiring its basic structure:

FEATURES

Low Supply Voltage Range: 1.8 V to 3.6 V

Ultra-Low Power Consumption

– Active Mode: 220 µA at 1 MHz, 2.2 V

– Standby Mode: 0.5 µA

– Off Mode (RAM Retention): 0.1 µA

Five Power-Saving Modes

Ultra-Fast Wake-Up From Standby Mode in Less Than 1 µs

16-Bit RISC Architecture, 62.5-ns Instruction Cycle Time

Basic Clock Module Configurations

– Internal Frequencies up to 16 MHz With Four Calibrated Frequencies

– Internal Very-Low-Power Low-Frequency (LF) Oscillator

– 32-kHz Crystal

– External Digital Clock Source One 16-Bit Timer_A With Three Capture/Compare Registers

Up to 16 Touch-Sense Enabled I/O Pins

Universal Serial Interface (USI) Supporting SPI and I2C

recover MCU IC Texas Instruments MSP430G2452IPW14R

recover MCU IC Texas Instruments MSP430G2452IPW14R

10-Bit 200-ksps Analog-to-Digital (A/D)

Converter With Internal Reference, Sample-and-Hold, and Autoscan (MSP430G2x52 Only)

On-Chip Comparator for Analog

Brownout Detector Serial Onboard Programming,

No External Programming Voltage Needed,

Programmable Code Protection by Security Fuse

On-Chip Emulation Logic With Spy-Bi-Wire Interface

Family Members are Summarized in Table 1 Package Options

– TSSOP: 14 Pin, 20 Pin

– PDIP: 20 Pin

– QFN: 16 Pin

For Complete Module Descriptions, See the MSP430x2xx Family User’s Guide (SLAU144)

Break Microcontroller TI TMS320F28232PGFA Protection

Break Microcontroller TI TMS320F28232PGFA Protection

Break Microcontroller TI TMS320F28232PGFA Protection

Break Microcontroller TI TMS320F28232PGFA Protection starts from understanding the technology and product features of it:

· High-Performance Static CMOS Technology

– Up to 150 MHz (6.67-ns Cycle Time)

– 1.9-V/1.8-V Core, 3.3-V I/O Design

· High-Performance 32-Bit CPU (TMS320C28x)

– IEEE-754 Single-Precision Floating-Point

Unit (FPU) (F2833x only)

– 16 x 16 and 32 x 32 MAC Operations

– 16 x 16 Dual MAC

– Harvard Bus Architecture

– Fast Interrupt Response and Processing

– Unified Memory Programming Model

– Code-Efficient (in C/C++ and Assembly)

· Six-Channel DMA Controller (for ADC, McBSP, ePWM, XINTF, and SARAM)

· 16-Bit or 32-Bit External Interface (XINTF)

– Over 2M x 16 Address Reach

· On-Chip Memory

– F28335, F28235:

256K x 16 Flash, 34K x 16 SARAM

– F28334, F28234:

128K x 16 Flash, 34K x 16 SARAM

– F28332, F28232:

64K x 16 Flash, 26K x 16 SARAM

– 1K x 16 OTP ROM

· Boot ROM (8K x 16)

– With Software Boot Modes (via SCI, SPI, CAN, I2C, McBSP, XINTF, and Parallel I/O)

– Standard Math Tables

· Clock and System Control

– Dynamic PLL Ratio Changes Supported

– On-Chip Oscillator

– Watchdog Timer Module

· GPIO0 to GPIO63 Pins Can Be Connected to One of the Eight External Core Interrupts

· Peripheral Interrupt Expansion (PIE) Block That Supports All 58 Peripheral Interrupts

· 128-Bit Security Key/Lock

– Protects Flash/OTP/RAM Blocks

– Prevents Firmware Reverse Engineering

· Enhanced Control Peripherals

– Up to 18 PWM Outputs

– Up to 6 HRPWM Outputs With 150 ps MEP Resolution

– Up to 6 Event Capture Inputs

– Up to 2 Quadrature Encoder Interfaces

– Up to 8 32-Bit Timers

(6 for eCAPs and 2 for eQEPs)

– Up to 9 16-Bit Timers

(6 for ePWMs and 3 XINTCTRs)

· Three 32-Bit CPU Timers

· Serial Port Peripherals

– Up to 2 CAN Modules

– Up to 3 SCI (UART) Modules

– Up to 2 McBSP Modules (Configurable as SPI)

– One SPI Module

– One Inter-Integrated-Circuit (I2C) Bus

· 12-Bit ADC, 16 Channels

– 80-ns Conversion Rate

– 2 x 8 Channel Input Multiplexer

– Two Sample-and-Hold

– Single/Simultaneous Conversions

– Internal or External Reference

· Up to 88 Individually Programmable, Multiplexed GPIO Pins With Input Filtering

· JTAG Boundary Scan Support (1)

· Advanced Emulation Features

– Analysis and Breakpoint Functions

– Real-Time Debug via Hardware

· Development Support Includes

– ANSI C/C++ Compiler/Assembler/Linker

– Code Composer Studio™ IDE

– DSP/BIOS™

– Digital Motor Control and Digital Power Software Libraries

Low-Power Modes and Power Savings from Break Microcontroller TI TMS320F28232PGFA Protection

– IDLE, STANDBY, HALT Modes Supported

– Disable Individual Peripheral Clocks

· Endianness: Little Endian

· Package Options:

– Lead-free, Green Packaging

– Low-Profile Quad Flatpack (PGF, PTP)

– MicroStar BGA™ (ZHH)

– Plastic BGA (ZJZ)

Attack Microchip MCU Embeded Firmware

Attack Microchip MCU Embeded Firmware

Attack Microchip MCU protective system and extract Embedded Firmware from microcontroller memory, make Microchip MCU cloning unit by provide the same functions as masters;

Attack Microchip MCU protective system and extract Embedded Firmware from memory, make Microchip MCU cloning unit by provide the same functions as masters;

The removal of material is strongly anisotropic (directional). Only the surfaces hit by the ions are removed, sides perpendicular to their paths are not touched. Mechanical polishing is performed with the use of abrasive materials. The process is time-consuming and requires special machines to maintain the planarity of the surface.

From the inspection perspective, the advantages of using polishing over wet and dry etching techniques is the ability to remove layer by layer and view features in the area of interest within the same plane. It is especially useful on multilayer interconnect processes fabricated with advanced planarisation techniques.