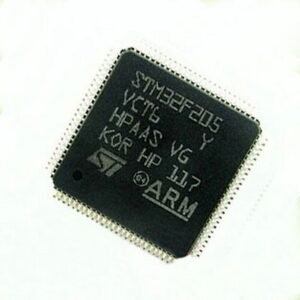

Reverse Secured STM32F205ZGT6 MCU Flash Program

Reverse Secured STM32F205ZGT6 MCU Flash Program

Reverse Secured STM32F205ZGT6 MCU Flash Program means the embedded heximal file can be readout directly from STM32F205ZGT6 Microcontroller flash memory, decrypt arm microprocessor stm32f205zgt6 memory file;

Reverse Secured STM32F205ZGT6 MCU Flash Program means the embedded heximal file can be readout directly from STM32F205ZGT6 Microcontroller flash memory, decrypt arm microprocessor stm32f205zgt6 memory file

The VBAT pin allows to power the device VBAT domain from an external battery or an external supercapacitor.

VBAT operation is activated when VDD is not present.

The VBAT pin supplies the RTC, the backup registers and the backup SRAM.

Note:

When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from VBAT operation.

When using WLCSP64+2 package, if IRROFF pin is connected to VDD, the VBAT

functionality is no more available and VBAT pin must be connected to VDD by recover arm microcontroller stm32f205rg flash code.

The STM32F20x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

Table 5 compares the features of the advanced-control, general-purpose and basic timers

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0- 100%) in the process of attacking stm32f205vb mcu protective fuse bit.

The TIM1 and TIM8 counters can be frozen in debug mode. Many of the advanced-control timer features are shared with those of the standard TIMx timers which have the same architecture. The advanced-control timer can therefore work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

Clone ARM STM32F205ZFT6 Microcontroller Firmware

Clone ARM STM32F205ZFT6 Microcontroller Firmware

Clone ARM STM32F205ZFT6 Microcontroller Firmware needs to readout mcu stmicroelectronics stm32f205zft6 heximal and copy flash memory embedded program to new stm32f205zft6 microprocessor;

Clone ARM STM32F205ZFT6 Microcontroller Firmware needs to readout mcu stmicroelectronics stm32f205zft6 heximal and copy flash memory embedded program to new stm32f205zft6 microprocessor;

The following conditions must be respected:

- VDD must always be higher than VCAP_1 and VCAP_2 to avoid current injection between power domains (see Figure 8).

- PA0 must be kept low to cover both conditions: until VCAP_1 and VCAP_2 reach 08 V, and until VDD reaches 1.7 V.

- NRST must be controlled by an external reset controller to keep the device under reset when VDD is below 7 V (see Figure 9).

In this mode, when the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is

- The brownout reset (BOR) circuitry is

- The embedded programmable voltage detector (PVD) is

VBAT functionality is no more available and VBAT pin must be connected to VDD.

The backup domain of the STM32F20x devices includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Its main features are the following:

- Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 day of the

- Programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby

- It is clocked by a 768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128 will recover arm microcontroller stm32f205rg flash code. The internal low-speed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

clone locked mcu chip STM32F205ZFT6 flash memory content after crack STM32F205ZFT6 microcontroller fuse bit

- Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours when attacking stmicroelectronics stm32f205vb mcu protection.

- A 20-bit prescaler is used for the time base It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar

Locked MCU Chip STM32F205ZCT6 Program Restoration

Locked MCU Chip STM32F205ZCT6 Program Restoration

Locked MCU Chip STM32F205ZCT6 Program Restoration needs to crack stm32f205zct6 processor protective resistance system firstly then extract stm32f205zct6 microcontroller flash memory content;

Locked MCU Chip STM32F205ZCT6 Program Restoration needs to crack stm32f205zct6 processor protective resistance system firstly then extract stm32f205zct6 microcontroller flash memory content

This feature is available only on packages featuring the REGOFF pin. The regulator is disabled by holding REGOFF high. The regulator OFF mode allows to supply externally a V12 voltage source through VCAP_1 and VCAP_2 pins.

The two 2.2 µF ceramic capacitors must be replaced by two 100 nF decoupling capacitors. Refer to Figure 19: Power supply scheme.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor must be used to monitor the V12 of the logic power domain when breaking stm32f205rb flash memory protection. PA0 pin must be used for this purpose, and act as power-on reset on V12 power domain.

crack locked mcu chip STM32F205ZCT6 and copy embedded heximal firmware from microcontroller STM32F205ZCT6 flash memory

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset the part of the 2 V logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used at power-on As a consequence, PA0 and NRST pins must be managed separately if the debug connection at reset or pre-reset is required.

Regulator OFF / internal reset ON

On WLCSP64+2 package, this mode is activated by connecting REGOFF pin to VDD and IRROFF pin to VSS. On UFBGA176 package, only REGOFF must be connected to VDD (IRROFF not available). In this mode, VDD/VDDA minimum value is 1.8 V to recover stm32f205rc microcontroller flash memory heximal.

The regulator OFF / internal reset ON mode allows the user to supply externally a 1.2 V voltage source through VCAP_1 and VCAP_2 pins, in addition to VDD.

Reverse Engineering STM32F205ZE Microcontroller Heximal Code

Reverse Engineering STM32F205ZE Microcontroller Heximal Code

Reverse Engineering STM32F205ZET6 Microcontroller Heximal Code and readout embedded heximal file from STM32F205ZET6 MCU flash memory, copy firmware to new Microprocessor stm32f205zet6;

Reverse Engineering STM32F205ZET6 Microcontroller Heximal Code and readout embedded heximal file from STM32F205ZET6 MCU flash memory, copy firmware to new Microprocessor stm32f205zet6

The device remains in reset mode when VDD is below a specified threshold, VPOR/PDR or VBOR, without the need for an external reset circuit. On devices in WLCSP64+2 package, the BOR, POR and PDR features can be disabled by setting IRROFF pin to VDD. In this mode an external power supply supervisor is required (see Section 3.16).

The devices also feature an embedded programmable voltage detector (PVD) that monitors the VDD/VDDA power supply and compares it to the VPVD threshold. An interrupt can be generated when VDD/VDDA drops below the VPVD threshold and/or when VDD/VDDA is higher than the VPVD threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

Código heximal del microcontrolador STM32F205ZET6 de ingeniería inversa y lectura del archivo heximal integrado de la memoria flash MCU STM32F205ZET6, copia del firmware al nuevo microprocesador stm32f205zet6

The regulator ON modes are activated by default on LQFP packages.On WLCSP64+2 package, they are activated by connecting both REGOFF and IRROFF pins to VSS, while only REGOFF must be connected to VSS on UFBGA176 package (IRROFF is not available).

VDD minimum value is 1.8 V.

break arm controller stm32f205zet6 fuse bit and extract embedded heximal file from mcu chip’s flash memory

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode

- LPR is used in Stop modes

The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby

The Power-down mode is activated only when entering Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost).

Two external ceramic capacitors must be connected on VCAP_1 and VCAP_2 pin. Refer to

Figure 19: Power supply scheme and Table 16: VCAP1/VCAP2 operating conditions.

All packages have the regulator ON feature.

Break STM32F205VCT6 MCU Chip Flash Memory

Break STM32F205VCT6 MCU Chip Flash Memory

Break STM32F205VCT6 MCU Chip Flash Memory needs to crack stm32f205vct6 arm mcu protective system, copy embedded flash program to new microcontroller stm32f205vct6;

Break STM32F205VCT6 MCU Chip Flash Memory needs to crack stm32f205vct6 arm mcu protective system, copy embedded flash program to new microcontroller stm32f205vct6

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code when breaking stm32f205rbt6 mcu flash memory protection.

romper STM32F205VCT6 La memoria flash del chip MCU necesita descifrar stm32f205vct6 armar el sistema de protección mcu, copiar el programa flash integrado al nuevo microcontrolador stm32f205vct6

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

The FSMC is embedded in all STM32F20x devices. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR Flash and NAND Flash.

Functionality overview:

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- Maximum frequency (fHCLK) for external access is 60 MHz

LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces by recover stm32f205rct6 mcu flash memory program. This LCD parallel interface capability makes it easy to build cost- effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

Attack STMicroelectronics STM32F205VB MCU Protection

Attack STMicroelectronics STM32F205VB MCU Protection

Attack STMicroelectronics STM32F205VB MCU Protection and unlock stm32f205vbt6 secured microcontroller flash program file after copy flash heximal file to stm32f205vb arm chip;

Attack STMicroelectronics STM32F205VB MCU Protection and unlock stm32f205vbt6 secured microcontroller flash program file after copy flash heximal file to stm32f205vb arm chip

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard by breaking arm mcu chip stm32f205rb flash memory, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

ataque STMicroelectronics STM32F205VB MCU protección y desbloqueo stm32f205vbt6 archivo de programa flash del microcontrolador seguro después de copiar el archivo flash heximal al chip arm stm32f205vb

All STM32F20x products embed:

- Up to 128 Kbytes of system SRAM accessed (read/write) at CPU clock speed with 0 wait states

- 4 Kbytes of backup

The content of this area is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They share some centralized FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

ARM Microcontroller STM32F205RG Flash Code Recovery

ARM Microcontroller STM32F205RG Flash Code Recovery

ARM Microcontroller STM32F205RG Flash Code Recovery starts from crack mcu chip stm32f205rg protective system and then decode secured flash memory software from microprocessor stm32f205rg;

ARM Microcontroller STM32F205RG Flash Code Recovery starts from crack mcu chip stm32f205rg protective system and then decode secured flash memory software from microprocessor stm32f205rg;

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

La recuperación del código flash del microcontrolador ARM STM32F205RG comienza desde el sistema de protección crack mcu chip stm32f205rg y luego decodifica el software de memoria flash seguro del microprocesador stm32f205rg

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real- time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it. The STM32F20x devices embed a 128-bit wide Flash memory of 128 Kbytes, 256 Kbytes, 512 Kbytes, 768 Kbytes or 1 Mbyte available for storing programs and data. The devices also feature 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys.

Attack ARM STM32F205RF Microprocessor Tamper Resistance

Attack ARM STM32F205RF Microprocessor Tamper Resistance

Attack ARM STM32F205RF Microprocessor Tamper Resistance and decode stm32f205rf secured memory software from its flash, then read out microcontroller stm32f205rf flash memory content;

Attack ARM STM32F205RF Microprocessor Tamper Resistance and decode stm32f205rf secured memory software from its flash, then read out microcontroller stm32f205rf flash memory content;

The Arm® Cortex®-M3 processor is the latest generation of processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption by recovering stm32f205rc microcontroller flash heximal, while delivering outstanding computational performance and an advanced response to interrupts.

The Arm® Cortex®-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an Arm core in the memory size usually associated with 8- and 16-bit devices. With its embedded Arm® core, the STM32F20x family is compatible with all Arm® tools and software.

Ataque la resistencia a la manipulación del microprocesador ARM STM32F205RF y decodifique el software de memoria protegida stm32f205rf desde su flash, luego lea el contenido de la memoria flash del microcontrolador stm32f205rf

The ART Accelerator™ is a memory accelerator which is optimized for STM32 industry- standard Arm® Cortex®-M3 processors. It balances the inherent performance advantage of the Arm® Cortex®-M3 over Flash memory technologies to break off stm32f205rb mcu flash memory, which normally requires the processor to wait for the Flash memory at higher operating frequencies.

unlock protected STM32F205RFT6 microprocessor fuse bit and readout embedded firmware from mcu chip STM32F205RFT6 flash memory

To release the processor full 150 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache which increases program execution speed from the 128-bit Flash memory. Based on CoreMark® benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 120 MHz.

Restoring ARM STM32F205RE MCU Flash Firmware

Restoring ARM STM32F205RE MCU Flash Firmware

Restoring ARM STM32F205RE MCU Flash Firmware starts from decrypt ARM STM32F205RE microcontroller flash memory program and then readout embedded code from microprocessor stm32f205re flash memory;

Restoring ARM STM32F205RE MCU Flash Firmware starts from decrypt ARM STM32F205RE microcontroller flash memory program and then readout embedded code from microprocessor stm32f205re flash memory

For the LQFP100 package, only FSMC Bank1 or Bank2 are Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio on devices in WLCSP64+2 package for arm stm32f205rc mcu flash memory heximal recovery, if IRROFF is set to VDD, the supply voltage can drop to 7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor.

взломать защищенный mcu stm32f205ret6 и скопировать программу flash heximal memory из прошивки микропроцессора stm32f205ret6

The STM32F205xx constitute the STM32F20x family, whose members are fully pin-to-pin, software and feature compatible, allowing the user to try different memory densities and peripherals for a greater degree of freedom during the development cycle.

The STM32F205xx and STM32F207xx devices maintain a close compatibility with the whole STM32F10xxx family. All functional pins are pin-to-pin compatible. The STM32F205xx and STM32F207xx, however, are not drop-in replacements for the STM32F10xxx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xxx to the STM32F20x family remains simple as only a few pins are impacted.

ARM STM32F205RC Microcontroller Flash Memory Heximal Recovery

ARM STM32F205RC Microcontroller Flash Memory Heximal Recovery

ARM STM32F205RC Microcontroller Flash Memory Heximal Recovery starts from decrypting arm mcu stm32f205rc embedded memory program and then clone flash memory code to new mcu stm32f205rc;

ARM STM32F205RC Microcontroller Flash Memory Heximal Recovery starts from decrypting arm mcu stm32f205rc embedded memory program and then clone flash memory code to new mcu stm32f205rc;

The STM32F205xx and STM32F207xx devices operate in the –40 to +105 °C temperature range from a 1.8 V to 3.6 V power supply. On devices in WLCSP64+2 package, if IRROFF is set to VDD, the supply voltage can drop to 1.7 V when the device operates in the 0 to

70 °C temperature range using an external power supply supervisor (see Section 3.16).

A comprehensive set of power-saving modes enables the design of low-power applications.

STM32F205xx and STM32F207xx devices are offered in various packages, ranging from 64 to 176 pins. The set of included peripherals changes with the chosen device when recovering ic chip stm32f107rct6 code.These features make the STM32F205xx and STM32F207xx microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

- For the LQFP100 package, only FSMC Bank1 or Bank2 are Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

- The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio when breaking stm32f101c4 binary file;

- On devices in WLCSP64+2 package, if IRROFF is set to VDD, the supply voltage can drop to 7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).