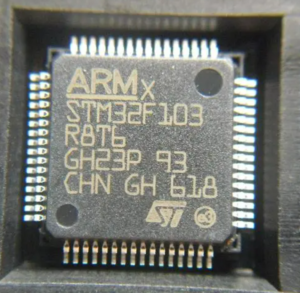

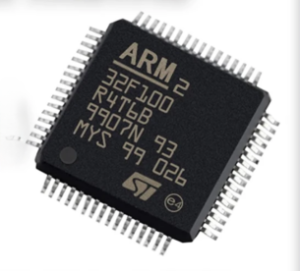

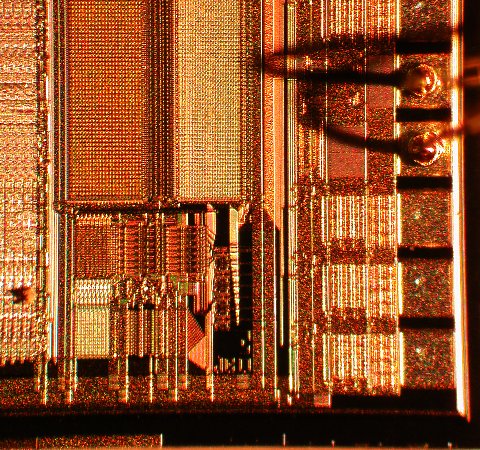

Recovering ARM Microprocessor STM32F103CB Flash Program

Recovering ARM Microprocessor STM32F103CB Flash Program

Recovering ARM Microprocessor STM32F103CB Flash Program after crack mcu stm32f103cb security fuse bit and disable the protection over the memory content, copy extracted firmware to new MCU;

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator by Crack STM32F103CB Microcontroller Flash Memory. All the information given in this paragraph are based on characterization results obtained with typical external components specified in below Table.

In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics when break arm mcu stm32f101cb flash memory (frequency, package, accuracy).

For CL1 and CL2 it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator when Break IC Flash. CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2.

Restoring ARM Microcontroller STM32F103C4 Flash Binary

Restoring ARM Microcontroller STM32F103C4 Flash Binary

Restoring ARM Microcontroller STM32F103C4 Flash Binary after crack locked mcu stm32f103c4 security fuse bit and copy extracted firmware to new Microcontroller;

The temperature sensor has to generate a voltage that varies linearly with temperature to Recover MCU content. The conversion range is between 2 V < VDDA < 3.6 V. The temperature sensor is internally connected to the ADC1_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target of STMicro STM32F101RB MCU flash memory breaking. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

Unless otherwise specified the minimum and maximum values in the process of Unlock ARM Base STM32F101CB Microprocessor are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at TA = 25 °C and TA = TAmax (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean±3S).

Unless otherwise specified, typical data are based on TA = 25 °C, VDD = 3.3 V (for the 2 V £ VDD £ 3.6 V voltage range). They are given only as design guidelines and are not tested.

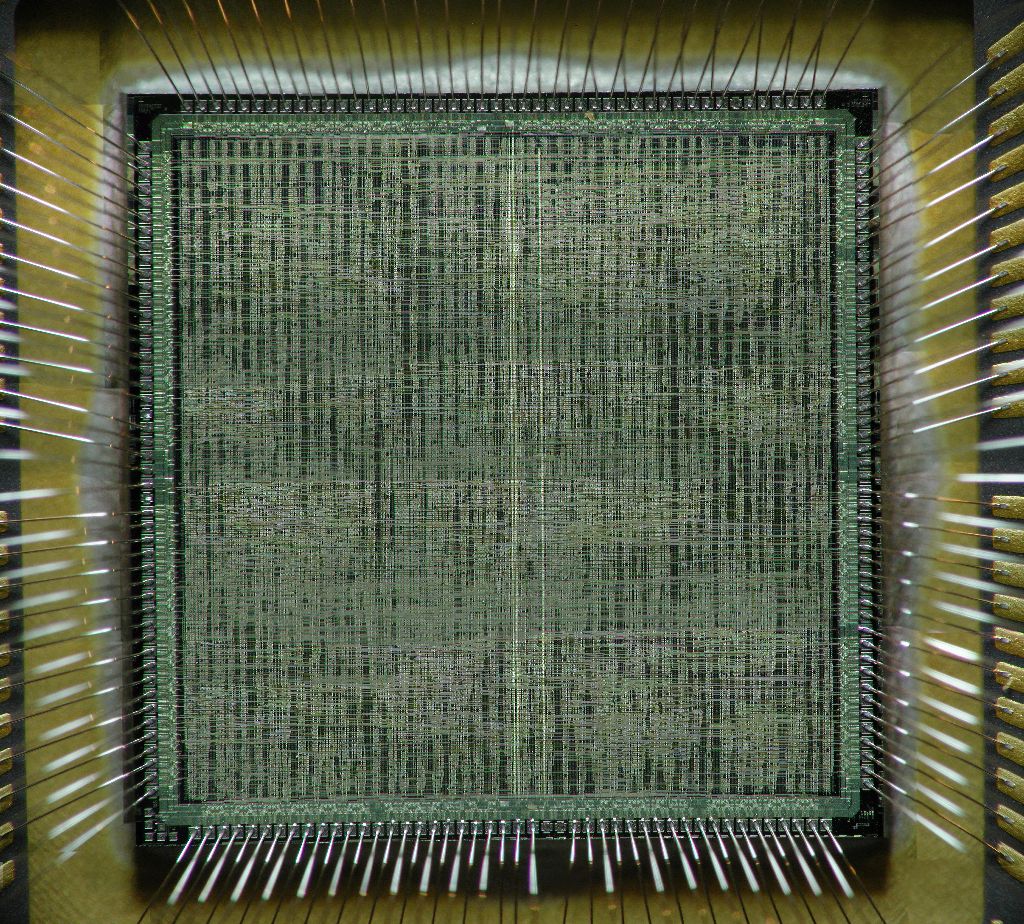

Duplicate ARM MCU STM32F101CB Memory Content

Duplicate ARM MCU STM32F101CB Memory Content

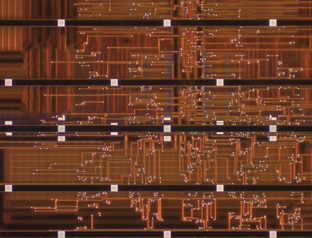

Duplicate ARM MCU STM32F101CB Memory Content include the program of locked flash memory and data of locked eeprom memory, the tamper resistance system of microcontroller stm32f101cb will be unlocked and embedded binary will extracted from MCU;

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on 6 channels which can provide great benefit to Unlock ARM Base STM32F101CB Microprocessor. It has complementary PWM outputs with programmable inserted dead times to Copy microcontroller. It can also be seen as a complete general-purpose timer. The 4 independent channels can be used for:

il contenuto della memoria STM32F101CB dell’MCU ARM duplicato include il programma della memoria flash bloccata e i dati della memoria eeprom bloccata, il sistema di resistenza alle manomissioni del microcontrollore stm32f101cb verrà sbloccato e il binario incorporato verrà estratto dall’MCU;

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes)

- One-pulse mode output

The counter can be frozen in debug mode. Many features are shared with those of the standard TIM timers which have the same architecture. The advanced control timer can therefore work together with the TIM timers via the Timer Link feature for synchronization or event chaining to facilitate the progress of recovering locked Microcontroller stm32f101c4 embedded firmware.

There are six synchronizable general-purpose timers embedded in the STM32F100xx devices. Each general-purpose timers can be used to generate PWM outputs, or as simple time base. STM32F100xx devices feature three synchronizable 4-channels general-purpose timers.

дубльований вміст пам’яті ARM MCU STM32F101CB включає програму заблокованої флеш-пам’яті та дані заблокованої пам’яті eeprom, систему захисту від несанкціонованого доступу мікроконтролера STM32F101CB буде розблоковано, а вбудований двійковий файл буде витягнуто з MCU;

These timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

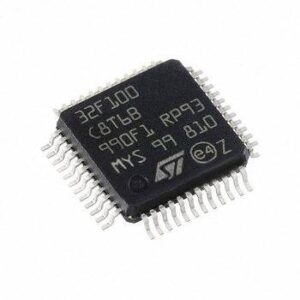

ARM Microcontroller STM32F101C4 Locked Firmware Recovery

ARM Microcontroller STM32F101C4 Locked Firmware Recovery

ARM Microcontroller STM32F101C4 Locked Firmware Recovery starts from cracking mcu stm32f101c4 flash memory and extract IC source code;

The STM32F101C4 value line embeds a nested vectored interrupt controller able to handle up to 41 maskable interrupt channels by Crack STM32F101C4 Microprocessor Flash Memory (not including the 16 interrupt lines of Cortex™-M3) and 16 priority levels.

Closely coupled NVIC gives low latency interrupt processing

Interrupt entry vector table address passed directly to the core

Closely coupled NVIC core interface

Allows early processing of interrupts

Processing of late arriving higher priority interrupts

Support for tail-chaining

Processor state automatically saved

Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency in the process of breaking arm mcu stm32f101rb flash memory.

Il ripristino del firmware bloccato STM32F101C4 del microcontrollore ARM inizia dal cracking della memoria flash MCU stm32f101c4 ed estrae il codice sorgente IC;

The external interrupt/event controller consists of 18 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently.

Відновлення заблокованої мікропрограми мікроконтролера ARM STM32F101C4 починається зі злому флеш-пам’яті MCU STM32F101C4 і вилучення вихідного коду IC;

A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

Break ARM Microcontroller STM32F101RB Flash Memory

Break ARM Microcontroller STM32F101RB Flash Memory

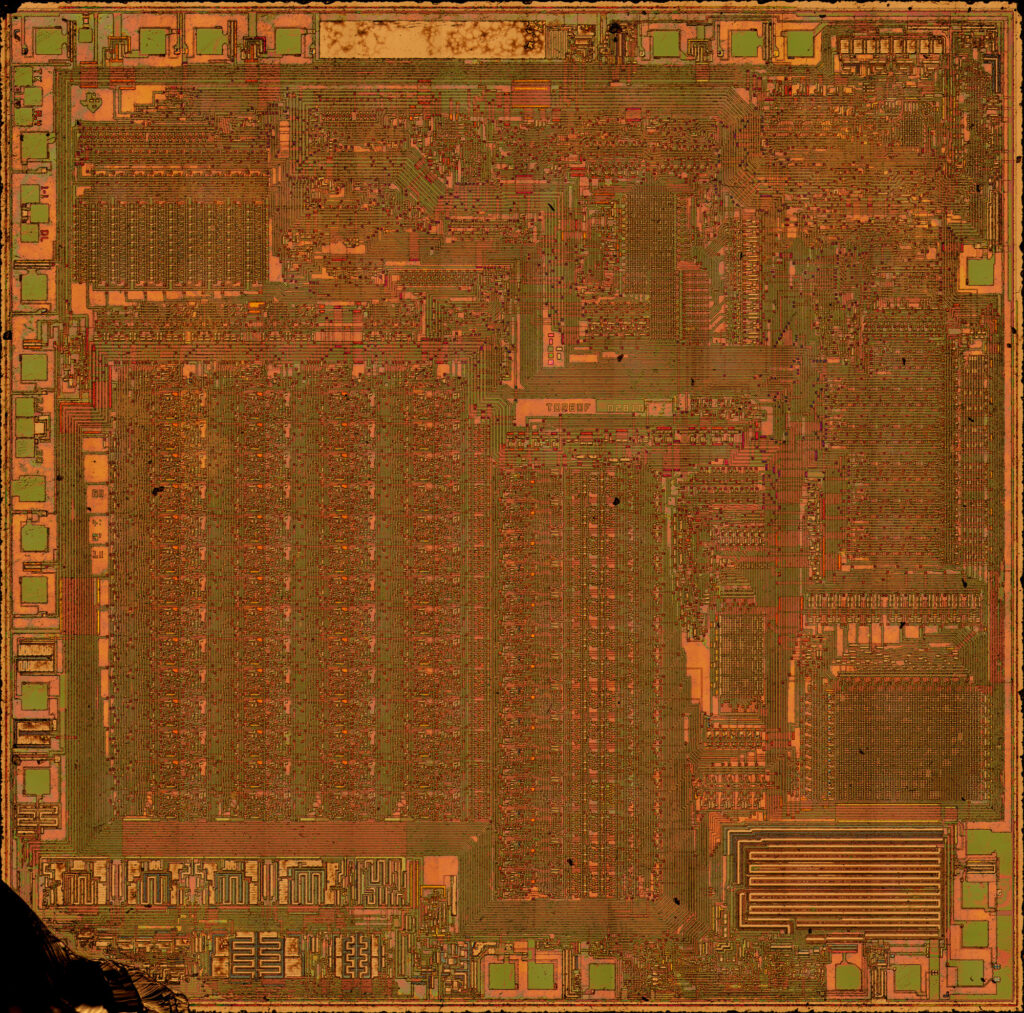

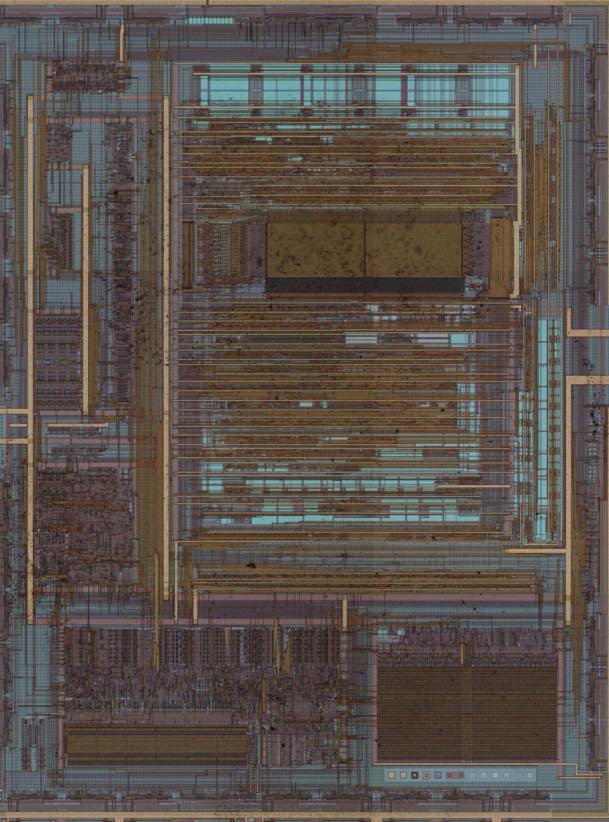

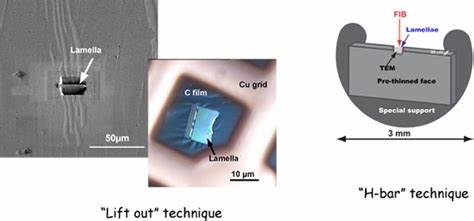

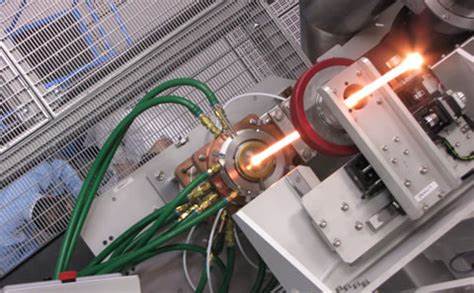

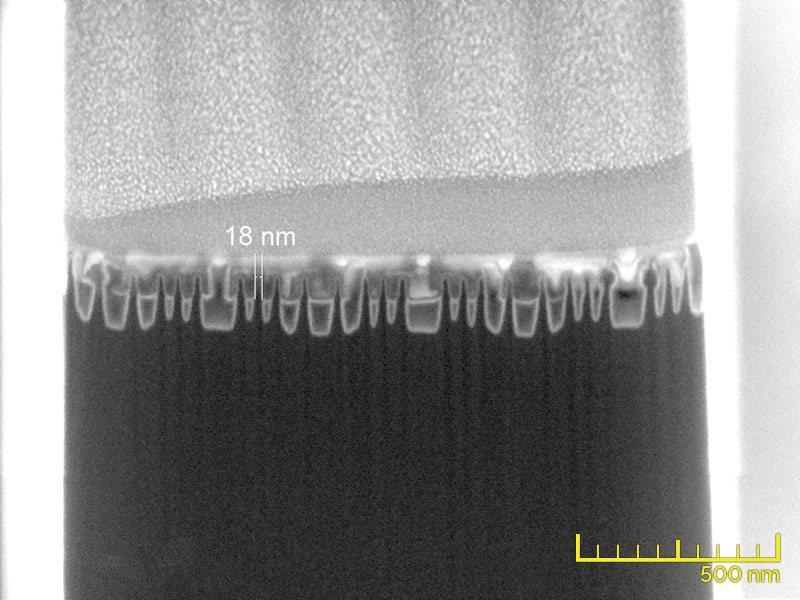

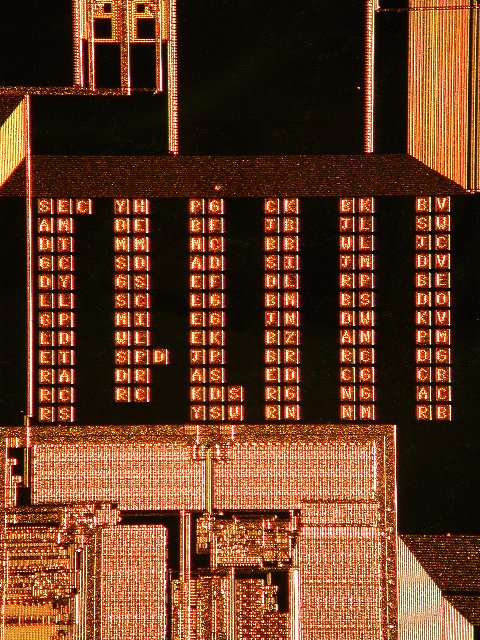

Break ARM Microcontroller STM32F101RB Flash Memory and copy heximal from embedded MCU to new fresh memory, cracking stm32f101rb security fuse bit needs to apply the focus ion beam technique;

The TIM2, TIM3, TIM4 general-purpose timers can work together or with the TIM1 advanced-control timer via the Timer Link feature for synchronization or STMicro STM32F101RB MCU Cracking.

TIM2, TIM3, TIM4 all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors to facilitate the progress of IC breaking. Their counters can be frozen in debug mode.

Rompi il microcontrollore ARM STM32F101RB memoria flash e copia esamale dall’MCU incorporato alla nuova memoria fresca, rompendo il bit del fusibile di sicurezza stm32f101rb per applicare la tecnica del fascio ionico di messa a fuoco …

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler by breaking arm mcu stm32f101c4 memory. TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining. TIM15 can be synchronized with TIM16 and TIM17.

зламати флеш-пам’ять мікроконтролера ARM STM32F101RB і скопіювати heximal із вбудованого мікроконтролера в нову свіжу пам’ять, зламати біт запобіжника безпеки stm32f101rb, потрібно застосувати техніку фокусування іонного променя

TIM15, TIM16, and TIM17 have a complementary output with dead-time generation and independent DMA request generation Their counters can be frozen in debug mode for the purpose of Crack MC68HC705J1 Microcontroller Memory. These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used as a watchdog to reset the device when a problem occurs in the process of MC68HC711PH8 Microcontroller Eprom Software Duplication, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

Attack Locked STM32F100R8 ARM MCU Flash Memory

Attack Locked STM32F100R8 ARM MCU Flash Memory

Attack Locked STM32F100R8 ARM MCU Flash Memory to extract microcontroller source code, and make microcontroller stm32f100r6 embedded firmware cloning;

STM32F100R8 power supply scheme will greatly improve the success rate of from its memory, hereby we will discuss and have better understanding about this process:

VDD = 2.0 to 3.6 V: External power supply for I/Os and the internal regulator. Provided externally through VDD

VSSA, VDDA = 0 to 3.6 V: External analog power supplies for ADC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC is used). VDDA and VSSA must be connected to VDD and VSS, respectively.

هجوم مقفل STM32F100R8 ذاكرة فلاش ARM MCU لاستخراج شفرة مصدر متحكم ، وجعل متحكم stm32f100r6 جزءا لا يتجزأ من استنساخ البرامج الثابتة ؛

VBAT = 1.8 to 3.6 V: Power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when VDD is not present.

The device has an integrated power on reset (POR)/power down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when VDD is below a specified threshold, VPOR/PDR, without the need for an external reset circuit to facilitate the process of arm CPU stm32f100r8 flash memory breaking.

The device features an embedded programmable voltage detector (PVD) that monitors the VDD/VDDA power supply and compares it to the VPVD threshold. An interrupt can be generated when VDD/VDDA drops below the VPVD threshold and/or when VDD/VDDA is higher than the VPVD threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

माइक्रोकंट्रोलर स्रोत कोड निकालने के लिए एआरएम एमसीयू फ्लैश मेमोरी STM32F100R8 हमला बंद, और माइक्रोकंट्रोलर STM32F100R8 एम्बेडेड फर्मवेयर क्लोनिंग बनाना;

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- l MR is used in the nominal regulation mode (Run)

- l LPR is used in the Stop mode

- l Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset to Break IC. It is disabled in Standby mode, providing high impedance output.

Recover STMicro STM32F100R4 Processor Flash Source Code

Recover STMicro STM32F100R4 Processor Flash Source Code

Recover STMicro STM32F100R4 Processor Flash Source Code from locked flash memory, crack arm microcontroller stm32f100r4 tamper resistance system and readout embedded firmware from MCU;

The STM32F100R4 value line embeds a nested vectored interrupt controller able to handle up to 41 maskable interrupt channels (not including the 16 interrupt lines of Cortex™-M3) and 16 priority levels which will affect Crack STM32F100R4 ARM Microcontroller process.

Closely coupled NVIC gives low latency interrupt processing

Interrupt entry vector table address passed directly to the core

Closely coupled NVIC core interface

Allows early processing of interrupts

Processing of late arriving higher priority interrupts

Support for tail-chaining

Processor state automatically saved

Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

استعادة STMicro STM32F100R4 شفرة مصدر فلاش المعالجات الدقيقة من ذاكرة فلاش مقفلة ، متحكم ذراع الكراك STM32F100R4 نظام مقاومة العبث وقراءة البرامج الثابتة المضمنة من MCU ؛

The external interrupt/event controller consists of 18 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently to provide better support in the process of restoring arm microprocessor stm32f100r8 program file.

A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-24 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator.

लॉक ्ड फ्लैश मेमोरी से एसटीमाइक्रो STM32F100R4 माइक्रोप्रोसेसर फ्लैश सोर्स कोड पुनर्प्राप्त करें, टैम्पर प्रतिरोध प्रणाली के STM32F100R4 आर्म माइक्रोकंट्रोलर को क्रैक करें और एमसीयू से रीडआउट एम्बेडेड फर्मवेयर;

A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency to Break IC memory, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 24 MHz.

Restore ARM Microprocessor STM32F100C8 Locked Program File

Restore ARM Microprocessor STM32F100C8 Locked Program File

Restore ARM Microprocessor STM32F100C8 Locked Program File and rewrite the firmware into to new STM32F100C8 as cloning unit, firmware from MCU STM32F100C8’s flash memory can be readout directly;

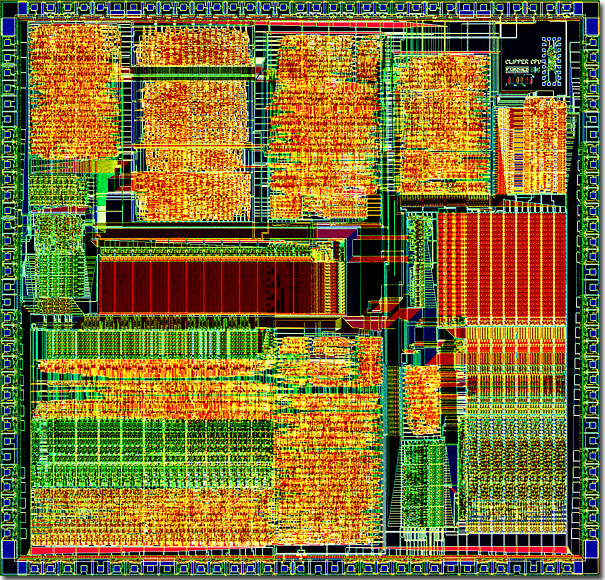

The ARM Cortex™-M3 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation through reverse engineering stmicro arm mcu stm32f100c6 memory, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex™-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

एआरएम माइक्रोप्रोसेसर STM32F100C8 लॉक किए गए प्रोग्राम फ़ाइल को पुनर्स्थापित करें और फर्मवेयर को क्लोनिंग यूनिट के रूप में नए STM32F100C8 में फिर से लिखें, एमसीयू STM32F100C8 की फ्लैश मेमोरी से फर्मवेयर को सीधे पढ़ा जा सकता है;

The STM32F100xx value line family having an embedded ARM core, is therefore compatible with all ARM tools and software.

Up to 128 Kbytes of embedded Flash memory is available for storing programs and data.

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

استعادة المعالجات الدقيقة ARM STM32F100C8 ملف البرنامج المقفل وإعادة كتابة البرامج الثابتة إلى STM32F100C8 جديدة كوحدة استنساخ ، يمكن قراءة البرامج الثابتة من ذاكرة فلاش MCU STM32F100C8 مباشرة ؛

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link- time and stored at a given memory location.

Up to 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

ARM Microcontroller STM32F100R6 Secured Flash Breaking

ARM Microcontroller STM32F100R6 Secured Flash Breaking

ARM Microcontroller STM32F100R6 Secured Flash Breaking needs to remove the security fuse bit protection over its flash and eeprom memory and readout the embedded firmware from locked processor;

STM32F100R6 power supply scheme will greatly improve the success rate of ARM Microcontroller STM32F100R6 Secured Flash Breaking, hereby we will discuss and have better understanding about this process:

VDD = 2.0 to 3.6 V: External power supply for I/Os and the internal regulator. Provided externally through VDD

VSSA, VDDA = 0 to 3.6 V: External analog power supplies for ADC, Reset blocks, RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC is used). VDDA and VSSA must be connected to VDD and VSS, respectively to execute Microchip PIC18LF452 MCU Code Cloning.

VBAT = 1.8 to 3.6 V: Power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when VDD is not present.

يحتاج متحكم ARM STM32F100R6 كسر الفلاش الآمن إلى إزالة حماية بت الصمامات الأمنية عبر فلاش STM32F100R6 MCU وذاكرة eeprom وقراءة البرامج الثابتة المضمنة من المعالج الدقيق المقفل واستنساخ شريحة MCU ؛

The device has an integrated power on reset (POR)/power down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when VDD is below a specified threshold, VPOR/PDR, without the need for an external reset circuit to facilitate the process of Restore DSP CPU TMS320F28030PAGT Source Code.

The device features an embedded programmable voltage detector (PVD) that monitors the VDD/VDDA power supply and compares it to the VPVD threshold. An interrupt can be generated when VDD/VDDA drops below the VPVD threshold and/or when VDD/VDDA is higher than the VPVD threshold for the purpose of Copy ARM MCU STMicroelectronics STM32F107RCT6. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

एआरएम माइक्रोकंट्रोलर STM32F100R6 सुरक्षित फ्लैश ब्रेकिंग को एमसीयू की STM32F100R6 फ्लैश और ईप्रोम मेमोरी पर सुरक्षा फ्यूज बिट सुरक्षा को हटाने और लॉक किए गए माइक्रोप्रोसेसर और क्लोन एमसीयू चिप से एम्बेडेड फर्मवेयर को पढ़ने की आवश्यकता है;

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- l MR is used in the nominal regulation mode (Run)

- l LPR is used in the Stop mode

- l Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset to Break IC. It is disabled in Standby mode, providing high impedance output.

Reverse Engineer STMicrco ARM MCU STM32F100C6

Reverse Engineer STMicrco ARM MCU STM32F100C6

Reverse Engineer STMicrco ARM MCU STM32F100C6 needs to unlock stm32f100c6’s security fuse bit and then extract embedded firmware from microcontroller’s flash and eeprom memory;

The STM32F100xx value line family incorporates the high-performance ARM Cortex™-M3 32-bit RISC core operating at a 24 MHz frequency which will be useful for Unlock ARM MCU STM32F100C6 Memory, high-speed embedded memories (Flash memory up to 128 Kbytes and SRAM up to 8 Kbytes), and an extensive range of enhanced peripherals and I/Os connected to two APB buses.

रिवर्स इंजीनियरिंग एसटीमाइक्रोको एआरएम एमसीयू STM32F100C6 को STM32F100C6 के सुरक्षा फ्यूज बिट को अनलॉक करने और फिर माइक्रोकंट्रोलर के फ्लैश और ईप्रोम मेमोरी से एम्बेडेड फर्मवेयर निकालने, समीपस्थ या बाइनरी के फर्मवेयर स्रोत कोड को नए माइक्रोकंट्रोलर STM32F100C6 में कॉपी करने की आवश्यकता होती है;

All devices offer standard communication interfaces (up to two I2Cs, two SPIs, one HDMI CEC, and up to three USARTs), one 12-bit ADC, two 12-bit DACs, up to six general-purpose 16-bit timers and an advanced-control PWM timer for the purpose of MCU source code reverse engineering.

The STM32F100xx low- and medium-density value line family operates in the –40 to +85 °C and –40 to +105 °C temperature ranges, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

الهندسة العكسية STMicrco ARM MCU STM32F100C6 يحتاج إلى فتح بت الصمامات الأمنية STM32F100C6 ثم استخراج البرامج الثابتة المضمنة من فلاش متحكم دقيق وذاكرة EEPROM ، ونسخ شفرة مصدر البرامج الثابتة من heximal أو ثنائي إلى متحكم دقيق جديد STM32F100C6 ؛

The STM32F100xx value line family includes devices in three different packages ranging from 48 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family from the process of Crack Microcontroller IC TI 430G2452.

These features make the STM32F100xx value line microcontroller family from the process of Attack Microcontroller MCU Microchip PIC16F84A suitable for a wide range of applications:

Application control and user interface

Medical and handheld equipment

PC peripherals, gaming and GPS platforms

Industrial applications: PLC, inverters, printers, and scanners

Alarm systems, Video intercom, and HVAC