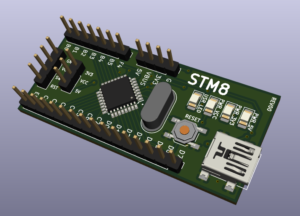

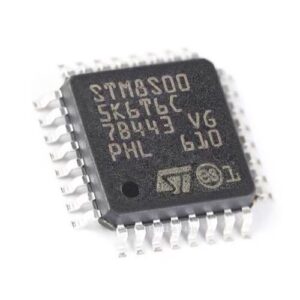

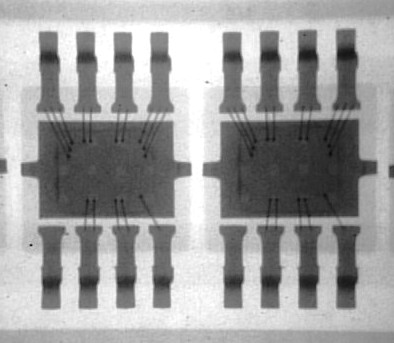

Secured Microcontroller STM8S207K8T6 Flash Heximal Code Unlocking

Secured Microcontroller STM8S207K8T6 Flash Heximal Code Unlocking

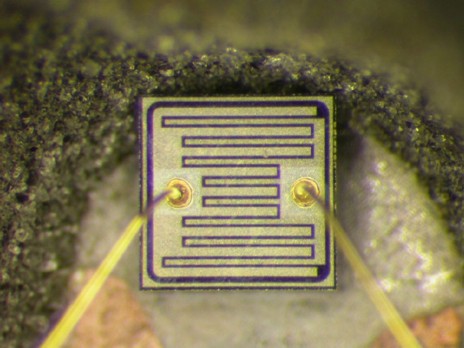

Secured Microcontroller STM8S207K8T6 Flash Heximal Code Unlocking will be able to reset the MCU status and readout software from stm8s207k8 program flash memory directly, the fuse bit of processor’s stm8s207k8 will be cracked by focus ion beam;

Susceptibility tests are performed on a sample basis during product characterization.

Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

ESD: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

güvenli mikrodenetleyici STM8S207K8T6 flaş onaltılık kod kilidini açma, MCU durumunu sıfırlayabilecek ve yazılımı doğrudan stm8s207k8 program flash belleğinden okuyabilecek, işlemcinin stm8s207k8’inin sigorta biti odak iyon ışını ile kırılacaktır;

FTB: A burst of fast transient voltage (positive and negative) is applied to VDD and VSS through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard which is an important fact for reversing stm8s005 mcu flash memory code.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709 (EMC design guide for STM microcontrollers).

Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular by recovering stm8s005k6 microcontroller data eeprom content.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

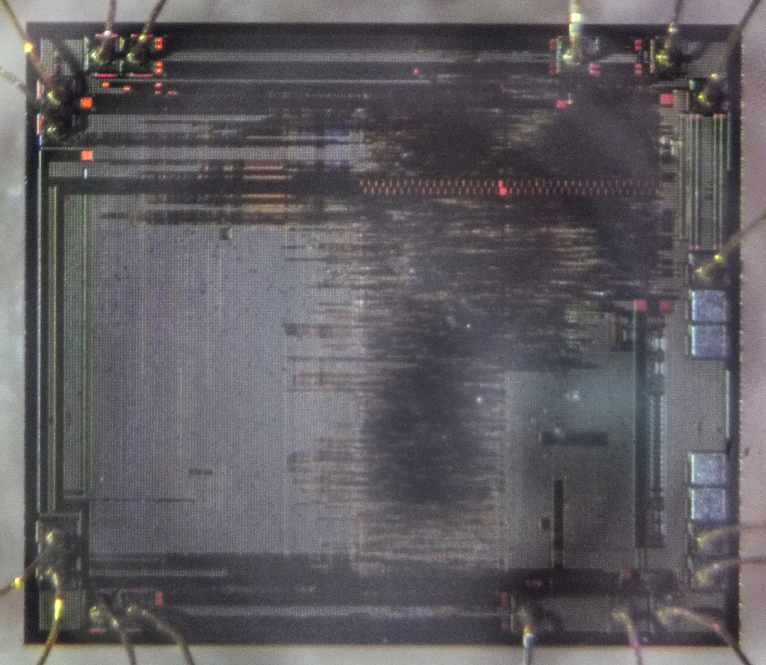

STMicro STM8S207S8 microprocessor reverse engineering

STMicro STM8S207S8 microprocessor reverse engineering

STMicro STM8S207S8 microprocessor reverse engineering can help engineer to break mcu stm8s207s8 protection and restore microcontroller stm8s207s8 memory program from flash and data from eeprom;

STMicro STM8S207S8 microprocessor reverse engineering can help engineer to break mcu stm8s207s8 protection and restore microcontroller stm8s207s8 memory program from flash and data from eeprom;

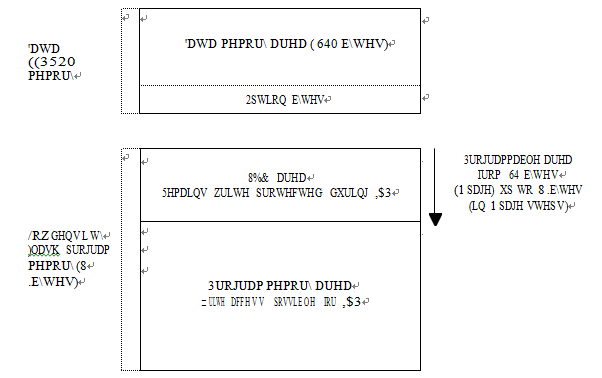

The read-out protection blocks reading and writing the Flash program memory and data EEPROM memory in ICP mode (and debug mode). Once the read-out protection is activated, any attempt to toggle its status triggers a global erase of the program and data memory.

Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller when recover stm8s003k3 flash memory heximal file.

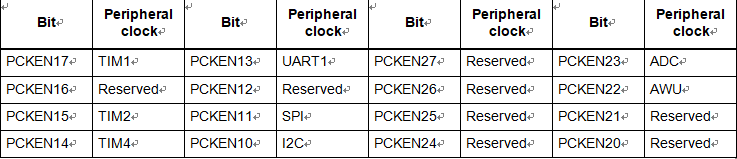

The clock controller distributes the system clock (fMASTER) coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness.

Clock prescaler: To get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

STMicro STM8S207S8 mikroişlemci tersine mühendisliği, mühendisin MCU STM8S207S8 korumasını kırmasına ve mikrodenetleyici STM8S207S8 bellek programını flaştan ve EEPROM’dan gelen verilerden geri yüklemesine yardımcı olabilir

Safe clock switching: Clock sources can be changed safely on the fly in run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

Clock management: To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

Master clock sources: Four different clock sources can be used to drive the master clock:

1-24 MHz high-speed external crystal (HSE)

Up to 24 MHz high-speed user-external clock (HSE user-ext)

16 MHz high-speed internal RC oscillator (HSI)

128 kHz low-speed internal RC (LSI)

Startup clock: After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts from cloning stm8s103f2 mcu memory source code.

Clock security system (CSS): This feature can be enabled by software. If an HSE clock failure occurs, the internal RC (16 MHz/8) is automatically selected by the CSS and an interrupt can optionally be generated.

Configurable main clock output (CCO): This outputs an external clock for use by the application.

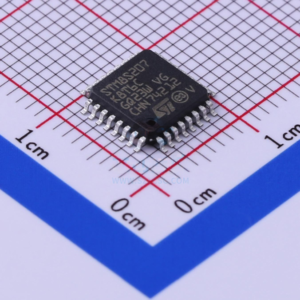

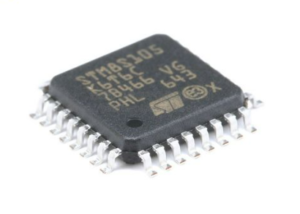

ST STM8S207K6 Locked Microcontroller Memory Breaking

ST STM8S207K6 Locked Microcontroller Memory Breaking

ST STM8S207K6 Locked Microcontroller Memory Breaking is a process to reverse engineering stm8s207k6 microcontroller structure and disable its protection and reset the status from locked to unlocked, copy embedded firmware from stm8s207k6 mcu flash content;

Write protection of Flash program memory and data EEPROM is provided to avoid unintentional overwriting of memory that could result from a user software malfunction.

There are two levels of write protection. The first level is known as MASS (memory access security system). MASS is always enabled and protects the main Flash program memory, data EEPROM and option bytes and we have to use technique to reverse mcu stm8s005c6 flash memory code.

ST STM8S207K6 gesperrter Mikrocontroller-Speicherbruch ist ein Prozess zum Reverse Engineering von STM8S207K6-Mikrocontrollern

Strukturieren und deaktivieren Sie den Schutz und setzen Sie den Status von gesperrt auf entsperrt zurück, kopieren Sie die eingebettete Firmware aus dem MCU-Flash-Inhalt STM8S207K6

To perform in-application programming (IAP), this write protection can be removed by writing a MASS key sequence in a control register. This allows the application to write to data EEPROM, modify the contents of main program memory or the device option bytes.

A second level of write protection, can be enabled to further protect a specific area of memory known as UBC (user boot code).

The size of the UBC is programmable through the UBC option byte, in increments of 1 page (512 bytes) by programming the UBC option byte in ICP mode when break mcu stm8s103f3 flash memory.

This divides the program memory into two areas:

Main program memory: Up to 128 Kbytes minus UBC

User-specific boot code (UBC): Configurable up to 128 Kbytes

The UBC area remains write-protected during in-application programming. This means that the MASS keys do not unlock the UBC area. It protects the memory used to store the boot program, specific code libraries, reset and interrupt vectors, the reset routine and usually the IAP and communication routines.

Recover STM8S207C6 Secured Microcontroller Flash Heximal

Recover STM8S207C6 Secured Microcontroller Flash Heximal

Recover STM8S207C6 Secured Microcontroller Flash Heximal from memory after crack mcu stm8s207c6 security fuse bit and readout embedded firmware from microprocessor stm8s207c6 memory;

The STM8S20xxx performance line 8-bit microcontrollers offer from 32 to 128 Kbytes Flash program memory. They are referred to as high-density devices in the STM8S microcontroller family reference manual.

All STM8S20xxx devices provide the following benefits: reduced system cost, performance robustness, short development cycles, and product longevity.

Stellen Sie den gesicherten Mikrocontroller-Flash-Speicher STM8S207C6 aus dem Speicher wieder her, nachdem das Sicherheitssicherungsbit der MCU STM8S207C6 geknackt und die eingebettete Firmware aus dem Speicher des Mikroprozessors STM8S207C6 ausgelesen wurde.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, watchdog, and brown-out reset which become important reason to break stm8s103k3 mcu protection.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals.

Full documentation is offered with a wide choice of development tools. Product longevity is ensured in the STM8S family thanks to their advanced core which is made in a state-of-the art technology for applications with 2.95 V to 5.5 V operating supply after breaking stm8s103f3 micro cpu flash memory.

Recover STM8S005K6T6 Microcontroller data Eeprom Content

Recover STM8S005K6T6 Microcontroller data Eeprom Content

Recover STM8S005K6T6 Microcontroller data Eeprom Content needs to crack fuse bit of stm8s005k6 secured memory and then extract heximal code from stm8s005k6 processor’s encrypted memory;

The clock controller distributes the system clock (fMASTER) coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness.

Clock prescaler: to get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler which can be used for clone microcontroller stm8s003f2 flash source code;

récupérer les données du microcontrôleur STM8S005K6T6, le contenu de l’eeprom doit craquer le bit de fusible de la mémoire sécurisée stm8s005k6, puis extraire le code hexadécimal de la mémoire chiffrée du processeur stm8s005k6 ;

Safe clock switching: clock sources can be changed safely on the fly in run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

Clock management: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

Master clock sources: four different clock sources can be used to drive the master clock:

1-16 MHz high-speed external crystal (HSE)

Up to 16 MHz high-speed user-external clock (HSE user-ext)

16 MHz high-speed internal RC oscillator (HSI)

128 kHz low-speed internal RC (LSI)

crack STM8S005K6T6 arm microcompute fuse bit and readout embedded firmware from flash and eeprom memory

Startup clock: After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts in the process of restore stm8s103k3 mcu chip embedded flash firmware.

Clock security system (CSS): This feature can be enabled by software. If an HSE clock failure occurs, the internal RC (16 MHz/8) is automatically selected by the CSS and an interrupt can optionally be generated.

Configurable main clock output (CCO): This outputs an external clock for use by the application.

Reverse MCU STM8S005C6T6 Flash Memory Code

Reverse MCU STM8S005C6T6 Flash Memory Code

Reverse MCU STM8S005C6T6 Flash Memory Code and readout embedded firmware from microprocessor stm8s005c6 memory, crack microcontroller stm8s005c6 fuse bit and remove its protective over the flash memory;

This divides the program memory into two areas:

Main program memory: up to 8 Kbyte minus UBC

User-specific boot code (UBC): Configurable up to 8 Kbyte

inversez le code de la mémoire flash MCU STM8S005C6T6 et lisez le micrologiciel intégré à partir de la mémoire du microprocesseur stm8s005c6, craquez le bit de fusible du microcontrôleur stm8s005c6 et retirez sa protection sur la mémoire flash ;

The UBC area remains write-protected during in-application programming. This means that the MASS keys do not unlock the UBC area when break stm8s103f3 micro cpu flash memory. It protects the memory used to store the boot program, specific code libraries, reset and interrupt vectors, the reset routine and usually the IAP and communication routines.

The read-out protection blocks reading and writing the Flash program memory and data EEPROM memory in ICP mode (and debug mode) which can be disable by breaking stm8s105 protective memory fuse bit.

Once the read-out protection is activated, any attempt to toggle its status triggers a global erase of the program and data memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

Hack STM8S105C6T3 Microprocessor Flash and Eeprom Memory

Hack STM8S105C6T3 Microprocessor Flash and Eeprom Memory

Hack STM8S105C6T3 Microprocessor Flash and Eeprom Memory needs to crack stm8s105 mcu protective system including remove its security fuse bit and then copy locked program from flash and eeprom memory of microcontroller;

Write protection of Flash program memory and data EEPROM is provided to avoid unintentional overwriting of memory that could result from a user software malfunction.

There are two levels of write protection. The first level is known as MASS (memory access security system) when reverse engineering stm8s105k6 data eeprom and program flash system. MASS is always enabled and protects the main Flash program memory, data EEPROM and option bytes.

pirater le flash du microprocesseur STM8S105C6T3 et la mémoire eeprom doit craquer le système de protection stm8s105 mcu, y compris retirer son bit de fusible de sécurité, puis copier le programme verrouillé à partir de la mémoire flash et eeprom du microcontrôleur ;

To perform in-application programming (IAP), this write protection can be removed by writing a MASS key sequence in a control register. This allows the application to write to data EEPROM, modify the contents of main program memory or the device option bytes to break mcu stm8s105k4 protective flash and eeprom memory.

A second level of write protection, can be enabled to further protect a specific area of memory known as UBC (user boot code). Refer to the figure below. The size of the UBC is programmable through the UBC option byte, in increments of 1 page (64-byte block) by programming the UBC option byte in ICP mode.

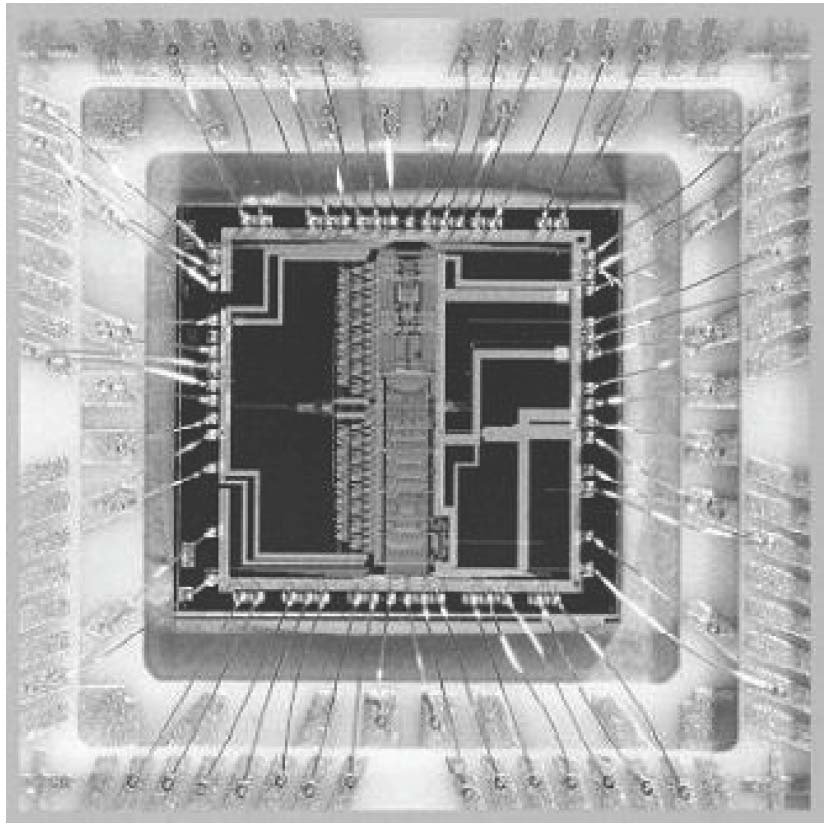

Reverse Engineering Microcontroller STM8S105K6U3 Structure

Reverse Engineering Microcontroller STM8S105K6U3 Structure

Reverse Engineering Microcontroller STM8S105K6U3 Structure can help us to figure out the security fuse bit of MCU stm8s105k6 location, then we can crack mcu stm8s105k6 memory protective system and readout embedded firmware from MCU;

Single wire interface module (SWIM) and debug module (DM)

The single wire interface module and debug module permits non-intrusive, real-time in- circuit debugging and fast memory programming.

SWIM

Single wire interface module for direct access to the debug module and memory programming. The interface can be activated in all device operation modes to copy stm8s003f3 mcu flash memory content, The maximum data transmission speed is 145 bytes/ms.

Debug module

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, also CPU operation can be monitored in real- time by means of shadow registers.

La structure du microcontrôleur d’ingénierie inverse STM8S105K6U3 peut nous aider à comprendre le bit de fusible de sécurité de l’emplacement du MCU stm8s105k6, puis nous pouvons craquer le système de protection de la mémoire mcu stm8s105k6 et lire le micrologiciel intégré du MCU

R/W to RAM and peripheral registers in real-time

R/W access to all resources by stalling the CPU

Breakpoints on all program-memory instructions (software breakpoints)

Two advanced breakpoints, 23 predefined configurations

Interrupt controller

Nested interrupts with three software priority levels,

32 interrupt vectors with hardware priority in the process of breaking microprocessor stm8s105k4 flash memory,

Up to 27 external interrupts on 6 vectors including TLI,

Trap and reset interrupts

Flash program and data EEPROM memory

8 Kbyte of Flash program single voltage Flash memory,

640 byte true data EEPROM,

User option byte area.

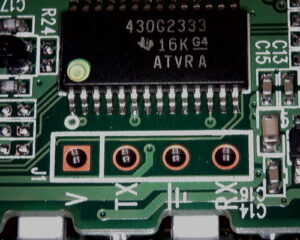

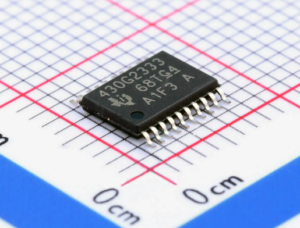

Texas MSP430G2333 Microcontroller Firmware Recovery

Texas MSP430G2333 Microcontroller Firmware Recovery

Texas MSP430G2333 Microcontroller Firmware Recovery needs to crack ti msp430g2333 microprocessor’s security tamper resistance system, and then extract microprocessor msp430g2333 locked code from its flash memory;

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Texas MSP430G2333 mikrodenetleyici ürün yazılımı kurtarma, ti msp430g2333 mikroişlemcinin güvenlik kurcalama direnci sistemini kırmalı ve ardından mikroişlemci msp430g2333 kilitli kodunu flash belleğinden çıkarmalıdır;

All voltages referenced to VSS. The JTAG fuse-blow voltage, VFB, is allowed to exceed the absolute maximum rating. The voltage is applied to the TEST pin when blowing the JTAG fuse which is a common method for cracking msp430g2230 mcu flash memory fuse bit.

Higher temperature may be applied during board soldering according to the current JEDEC J-STD-020 specification with peak reflow temperatures not higher than classified on the device label on the shipping boxes or reels.

The MSP430 CPU is clocked directly with MCLK. Both the high and low phase of MCLK must not exceed the pulse duration of the specified maximum frequency when restoring msp430g2001 microcontroller heximal program.

Modules might have a different maximum input clock specification. See the specification of the respective module in this data sheet.

Crack Texas Instrument MSP430G2230 MCU Flash Memory

Crack Texas Instrument MSP430G2230 MCU Flash Memory

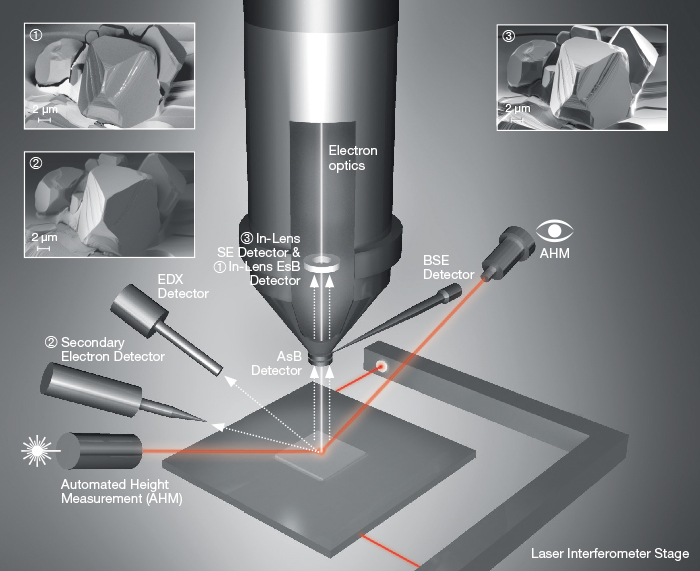

Crack Texas Instrument MSP430G2230 MCU Flash Memory needs to decapsulate MSP430G2230 by chemical solution and unlock microcontroller tamper resistance system, extract embedded source code from TI IC chip;

Universal Serial Communications Interface (USCI)

The USCI module is used for serial data communication. The USCI module supports synchronous communication protocols such as SPI (3 or 4 pin) and I2C, and asynchronous communication protocols such as UART, enhanced UART with automatic baudrate detection (LIN), and IrDA. Not all packages support the USCI functionality.

çatlak Texas Instrument MSP430G2230 MCU flash belleğin MSP430G2230’u kimyasal çözelti ile kapsülünü çözmesi ve mikrodenetleyici kurcalama direnci sisteminin kilidini açması, gömülü kaynak kodunu TI IC yongasından çıkarması gerekir

USCI_A0 provides support for SPI (3 or 4 pin), UART, enhanced UART, and IrDA. USCI_B0 provides support for SPI (3 or 4 pin) and I2C.

Comparator_A+

The primary function of the comparator_A+ module is to support precision slope analog-to-digital conversions, battery-voltage supervision, and monitoring of external analog signals.

ADC10 (MSP430G2x53 Only)

The ADC10 module supports fast 10-bit analog-to-digital conversions. The module implements a 10-bit SAR core, sample select control, reference generator, and data transfer controller (DTC) for automatic conversion result handling by replicating msp430g2231 cpu flash memory file, allowing ADC samples to be converted and stored without any CPU intervention.