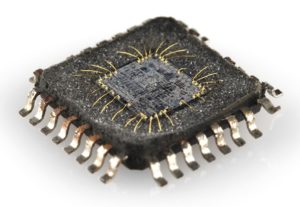

Recover MCU ATmega2561V Eeprom

Recover MCU ATmega2561V Eeprom

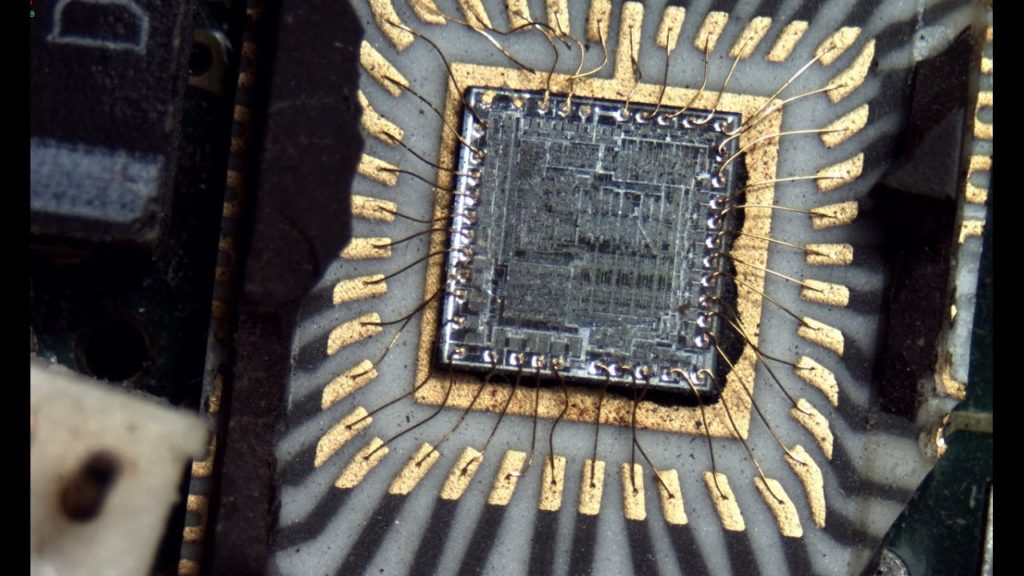

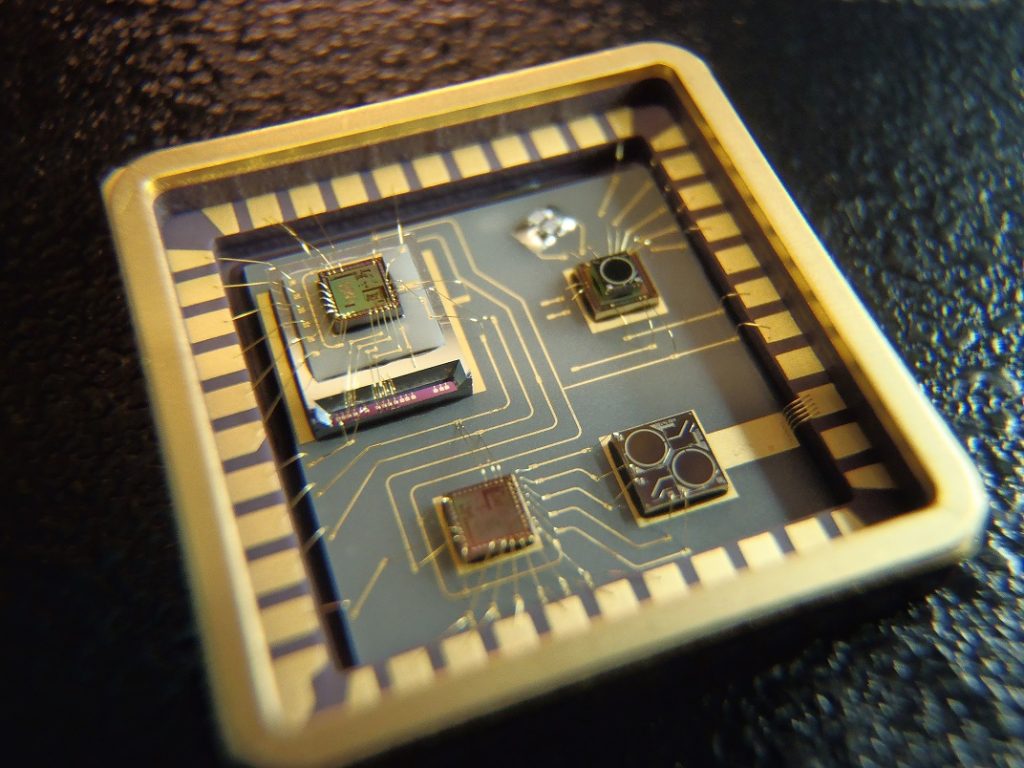

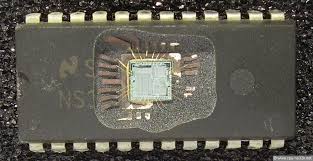

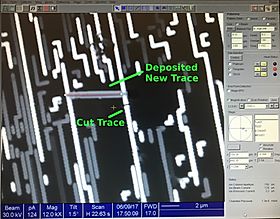

Recover MCU ATmega2561V Eeprom content needs to crack mcu atmega2561v protective system by focus ion beam and then copy the firmware inside flash and eeprom memory of microcontroller atmega2561v to new ones for same functionality;

This documentation contains simple code examples that briefly show how to use various parts of the device. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

These code examples assume that the part specific header file is included before compilation. For I/O registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR” if Recover atmega2560 MCU flash.

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts.

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory.

This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory. The fast-access Register File contains 32 x 8-bit general purpose working registers with a single clock cycle access time.

This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two operands are output from the Register File, the operation is executed, and the result is stored back in the Register File – in one clock cycle if Reverse engineering atmega1281 MCU.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for

Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the Status Register is updated to reflect information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot Program section and the Application Program section. Both sections have dedicated Lock bits for write and read/write protection. The SPM instruction that writes into the Application Flash memory section must reside in the Boot Program section.

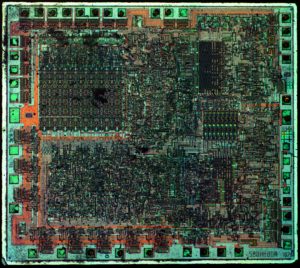

Break IC ATmega2561 Program

Break IC ATmega2561 Program

Break IC ATmega2561 and copy mcu atmega2561 Program from its flash memory, the security fuse bit of the microcontroller atmega2561 will be unlocked after the process;

The device is manufactured using Atmel’s high-density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core.

The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation if Break microcontroller pic16c65b eeprom.

By combining an 8-bit RISC CPU with In-System Self-Program mable Flash on a monolithic ch ip, the Atmel ATmega2561 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega2561 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits after recover mcu pic16f687 software.

Each device in the ATmeg2561 family differs only in memory size and number of pins. Table 1 summarizes the different configurations for the six devices.

Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated when copy microcontroller pic16f677 code.

The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running. Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated.

The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running. Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability.

As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

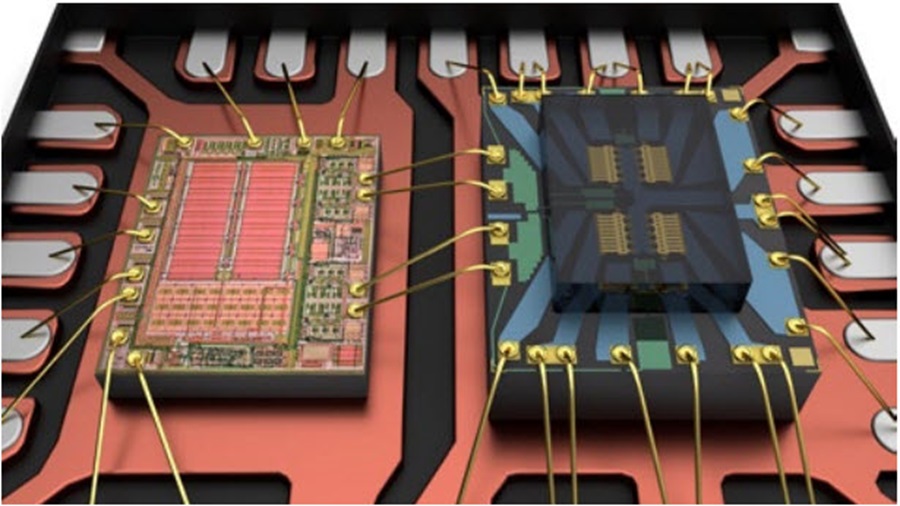

Recover MCU ATmega1281V Binary

Recover MCU ATmega1281V Binary

Recover MCU ATmega1281V Binary from secured program memory after crack microcontroller atmega1281v fuse bit and then copy firmware atmega1281v to new microprocessor;

The ATmega1281 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega1281v achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle if attack cpld xc9536xl.

The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega1281v provides the following features: 64K/128K/256K bytes of In-System Programmable Flash with Read-While-Write capabilities, 4K bytes EEPROM, 8K bytes SRAM, 54/86 general purpose I/O lines, 32 general purpose working registers after break cpld epm7064lc68.

Real Time Counter (RTC), six flexible Timer/Counters with compare modes and PWM, 4 USARTs, a byte oriented 2-wire Serial Interface, a 16-channel, 10-bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with Internal Oscillator, an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface.

Also used for accessing the On-MCU Debug system and programming and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning before break microcontroller msp430f4361.

The Power-down mode saves the register contents but freezes the Oscillator, disabling all other MCU functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping.

The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the Crystal/Resonator Oscillator is running while the rest of the device is sleeping.

This allows very fast start-up combined with low power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.

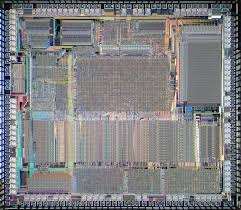

Reverse Engineering Microcontroller ATMEGA1281 Program

Reverse Engineering Microcontroller ATMEGA1281 Program

Reverse Engineering Microcontroller ATMEGA1281 purpose is to unlock mcu atmega1281 flash memory and then copy Program and data from atmega1281 memory to new MCU;

Features

High Performance, Low Power AVR® 8-Bit Microcontroller

Advanced RISC Architecture

– 135 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-Chip 2-cycle Multiplier

Non-volatile Program and Data Memories

– 64K/128K/256K Bytes of In-System Self-Programmable Flash

Endurance: 10,000 Write/Erase Cycles

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– 4K Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

– 8K Bytes Internal SRAM

– Up to 64K Bytes Optional External Memory Space

– Programming Lock for Software Security

JTAG (IEEE std. 1149.1 compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support when copy cpld epm9320arc208

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

– Four 16-bit Timer/Counter with Separate Prescaler, Compare- and Capture Mode

– Real Time Counter with Separate Oscillator

– Four 8-bit PWM Channels

– Six/Twelve PWM Channels with Programmable Resolution from 2 to 16 Bits (ATmega1281/2561, ATmega640/1280/2560)

– Output Compare Modulator

– 8/16-channel, 10-bit ADC

– Two/Four Programmable Serial USART (ATmega1281/2561,ATmega640/1280/2560)

– Master/Slave SPI Serial Interface

– Byte Oriented 2-wire Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator after Reverse engineering Microcontroller

– On-chip Analog Comparator

– Interrupt and Wake-up on Pin Change

Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated Oscillator

– External and Internal Interrupt Sources when Reverse engineering Microcontroller

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and Extended Standby

I/O and Packages

– 51/86 Programmable I/O Lines (ATmega1281/2561, ATmega640/1280/2560)

– 64-lead (ATmega1281/2561)

– 100-lead (ATmega640/1280/2560)

– 100-lead TQFP (64-lead TQFP Option)

Temperature Range:

– -40°C to 85°C Industrial if Reverse engineering Microcontroller

Speed Grade:

Programmable Flash

– ATmega1281/2561V/ATmega640/1280/2560V: 0 – 4 MHz @ 1.8 – 5.5V, 0 – 8 MHz @ 2.7 – 5.5V

– ATmega640/1280/1281/2560/2561: 0 – 8 MHz @ 2.7 – 5.5V, 0 – 16 MHz @ 4.5 – 5.5V before Reverse engineering Microcontroller

Recover MCU SN8P2608 Heximal

Recover MCU SN8P2608 Heximal

We can Recover MCU SN8P2608 Heximal, please view the Recover MCU SN8P2608 features for your reference:

The brown out reset is a power dropping condition. The power drops from normal voltage to low voltage by external factors (e.g. EFT interference or external loading changed). The brown out reset would make the system not work well or executing program error when Recover MCU .

The power dropping might through the voltage range that’s the system dead-band. The dead-band means the power range can’t offer the system minimum operation power requirement. The above diagram is a typical brown out reset diagram. There is a serious noise under the VDD, and VDD voltage drops very deep if Recover MCU .

There is a dotted line to separate the system working area. The above area is the system work well area. The below area is the system work error area called dead-band. V1 doesn’t touch the below area and not effect the system operation. But the V2 and V3 is under the below area and may induce the system error occurrence. Let system under dead-band includes some conditions before Recover MCU .

DC application:

The power source of DC application is usually using battery. When low battery condition and MCU drive any loading, the power drops and keeps in dead-band. Under the situation, the power won’t drop deeper and not touch the system reset voltage. That makes the system under dead-band after Recover MCU .

AC application:

In AC power application, the DC power is regulated from AC power source. This kind of power usually couples with AC noise that makes the DC power dirty. Or the external loading is very heavy, e.g. driving motor. The loading operating induces noise and overlaps with the DC power. VDD drops by the noise, and the system works under unstable power situation if Recover MCU .

The power on duration and power down duration are longer in AC application. The system power on sequence protects the power on successful, but the power down situation is like DC low battery condition. When turn off the AC power, the VDD drops slowly and through the dead-band for a while before Recover MCU .

To improve the brown out reset needs to know the system minimum operating voltage which is depend on the system executing rate and power level. Different system executing rates have different system minimum operating voltage after Recover MCU .

The electrical characteristic section shows the system voltage to executing rate relationship. Normally the system operation voltage area is higher than the system reset voltage to VDD, and the reset voltage is decided by LVD detect level if Recover MCU .

The system minimum operating voltage rises when the system executing rate upper even higher than system reset voltage. The dead-band definition is the system minimum operating voltage above the system reset voltage when Recover MCU .

Break IC PIC16C556A Software

Break IC PIC16C556A Software

Break IC PIC16C556A and make mcu pic16c556a clone which is provide the same functions as original one after read microcontroller Software from embedded memory;

Table 1-1 shows the features of the PIC16C55X(A) mid-range microcontroller families. A simplified block diagram of the PIC16C55X(A) is shown in Figure 3-1.

The PIC16C55X(A) series fit perfectly in applications ranging from motor control to low-power remote sensors. The EPROM technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations.

Low-cost, low-power, high-performance, ease of use and I/O flexibility make the PIC16C55X(A) very versatile.

Those users familiar with the PIC16C5X family of microcontrollers will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for PIC16C5X can be easily ported to PIC16C55X(A) family of devices (Appendix B).

The PIC16C55X(A) family fills the niche for users wanting to migrate up from the PIC16C5X family and not needing various peripheral features of other members of the PIC16XX mid-range microcontroller family.

The PIC16C55X(A) family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A “C” compiler and fuzzy logic support tools are also available.

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in the PIC16C55X(A) Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

Break IC SN8P2606 Binary

Break IC SN8P2606 Binary

We can Break IC SN8P2606 Binary, please view the IC SN8P2606 features for your reference:

The power on reset depend no LVD operation for most power-up situations. The power supplying to system is a rising curve and needs some time to achieve the normal voltage. Power on reset sequence is as following:

Power-up: System detects the power voltage up and waits for power stable.

External reset (only external reset pin enable): System checks external reset pin status. If external reset pin is not high level, the system keeps reset status and waits external reset pin released if Break IC SN8P2606 Binary.

System initialization: All system registers is set as initial conditions and system is ready.

Oscillator warm up: Oscillator operation is successfully and supply to system clock.

Program executing: Power on sequence is finished and program executes from ORG 0.

Watchdog reset is a system protection. In normal condition, system works well and clears watchdog timer by program.

Under error condition, system is in unknown situation and watchdog can’t be clear by program before watchdog timer overflow. Watchdog timer overflow occurs and the system is reset. After watchdog reset, the system restarts and returns normal mode. Watchdog reset sequence is as following.

Watchdog timer status: System checks watchdog timer overflow status. If watchdog timer overflow occurs, the system is reset before Break IC SN8P2606 Binary.

System initialization: All system registers is set as initial conditions and system is ready.

Oscillator warm up: Oscillator operation is successfully and supply to system clock.

Program executing: Power on sequence is finished and program executes from ORG 0 when Break IC SN8P2606 Binary.

Watchdog reset is a system protection. In normal condition, system works well and clears watchdog timer by program.

Under error condition, system is in unknown situation and watchdog can’t be clear by program before watchdog timer overflow. Watchdog timer overflow occurs and the system is reset. After watchdog reset, the system restarts and returns normal mode. Watchdog reset sequence is as following.

Watchdog timer status: System checks watchdog timer overflow status. If watchdog timer overflow occurs, the system is reset.

System initialization: All system registers is set as initial conditions and system is ready.

Oscillator warm up: Oscillator operation is successfully and supply to system clock.

Program executing: Power on sequence is finished and program executes from ORG 0. Watchdog timer application note is as following after Break IC SN8P2606 Binary.

Before clearing watchdog timer, check I/O status and check RAM contents can improve system error. Don’t clear watchdog timer in interrupt vector and interrupt service routine. That can improve main routine fail. Clearing watchdog timer program is only at one part of the program. This way is the best structure to enhance the watchdog timer function.

Break Chip PIC12CE518 Binary

Break Chip PIC12CE518 Binary

Break Chip PIC12CE518 Flash memory and read pic12ce518 mcu binary from embedded memory after copy the embedded code to new microcontroller;

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4- 8) if extract pic16f84 mcu firmware.

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared.

Instructions where the PCL is the destination, or Modify PCL instructions, include MOVWF PC, ADDWF PC, and BSF PC,5.

The Program Counter is set upon a RESET, which means that the PC addresses the last location in the last page i.e., the oscillator calibration instruction. After executing MOVLW XX, the PC will roll over to location 00h, and begin executing user code.

The STATUS register page preselect bits are cleared upon a RESET, which means that page 0 is pre-selected.

Therefore, upon a RESET, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered. PIC12C5XX devices have a 12-bit wide L.I.F.O. hardware push/pop stack.

A CALL instruction will push the current value of stack 1 into stack 2 and then push the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL’s are executed, only the most recent two return addresses are stored when crack mc68hc05b6 Chip.

ARETLW instruction will pop the contents of stack level 1 into the program counter and then copy stack level contents into level 1. If more than two sequential RETLW’s are executed, the stack will be filled with the address previously stored in level 2. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

Upon any reset, the contents of the stack remain unchanged, however the program counter (PCL) will also be reset to Break MCU Chip.

Copy Microcontroller PIC16F882 Heximal

Copy Microcontroller PIC16F882 Heximal

Copy Microcontroller PIC16F882 Heximal from flash memory and eeprom memory, unlock mcu pic16f882 protection and crack microcontroller pic16f882 security fuse bit to unleash embedded firmware.

High-Performance RISC CPU:

· Only 35 Instructions to Learn:

– All single-cycle instructions except branches

· Operating Speed:

– DC – 20 MHz oscillator/clock input

– DC – 200 ns instruction cycle

· Interrupt Capability

· 8-Level Deep Hardware Stack

· Direct, Indirect and Relative Addressing modes

Special Microcontroller Features:

· Precision Internal Oscillator:

– Factory calibrated to ±1%

– Software selectable frequency range of 8 MHz to 31 kHz

– Software tunable

– Two-Speed Start-up mode

– Crystal fail detect for critical applications

– Clock mode switching during operation for power savings

· Power-Saving Sleep mode

· Wide Operating Voltage Range (2.0V-5.5V)

· Industrial and Extended Temperature Range

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Brown-out Reset (BOR) with Software Control Option

· Enhanced Low-Current Watchdog Timer (WDT) with On-Chip Oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

· Multiplexed Master Clear with Pull-up/Input Pin

· Programmable Code Protection

· High Endurance Flash/EEPROM Cell:

– 100,000 write Flash endurance

– 1,000,000 write EEPROM endurance

– Flash/Data EEPROM retention: > 40 years

· Program Memory Read/Write during run time

· In-Circuit Debugger (on board)

Reverse Engineering Microcontroller ATMEGA2560V Firmware

Reverse Engineering Microcontroller ATMEGA2560V Firmware

We can Reverse engineering Microcontroller ATMEGA2560V Firmware, please view the Microcontroller ATMEGA2560V features for your reference:

The ATmega2560v implements 256 bytes of RAM. The upper 128 bytes of RAM occupy a parallel space to the Special Function Registers. That means the upper 128 bytes have the same addresses as the SFR space but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the address mode used in the instruction specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions that use direct addressing access SFR space.

For example, the following direct addressing instruction accesses the SFR at location 0A0H (which is P2). MOV 0A0H, #data

Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H) before Reverse Engineering Microcontroller ATMEGA2560V Firmware.

Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack, The programmable Watchdog Timer (WDT) operates from an independent oscillator. The prescaler bits, PS0, PS1 and PS2 in SFR WCON are used to set the period of the Watchdog Timer from 16 ms to 2048 ms.

The available timer periods are shown in the following table and the actual timer periods (at VCC = 5V) are within ±30% of the nominal. The WDT is disabled by Power-on Reset and during Power Down. It is enabled by setting the WDTEN bit in SFR WCON (address = 96H) after Reverse Engineering Microcontroller ATMEGA2560V Firmware.

The WDT is reset by setting the WDTRST bit in WCON. When the WDT times out without being reset or disabled, an internal RST pulse is generated to reset the CPU. Table 7. Watchdog Timer Period Selection space.

Timer 0 and Timer 1 in the AT89LS53 operate the same way as Timer 0 and Timer 1 in the AT89C51, AT89C52 and AT89C55. For further information, see the October 1995 Microcontroller Data Book, page 2-45, section titled, “Timer/Counters.”

Timer 2 is a 16 bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit C/T2 in the SFR T2CON (shown in Table 2). Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator before Reverse Engineering Microcontroller ATMEGA2560V Firmware.

The modes are selected by bits in T2CON, as shown in Table 8. Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented.

The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. To ensure that a given level is sampled at least once before it changes, the level should be held for at least one full machine cycle when Reverse Engineering Microcontroller ATMEGA2560V Firmware.