Microprocessor PIC18F2515 Heximal File Recovery

Microprocessor PIC18F2515 Heximal File Recovery

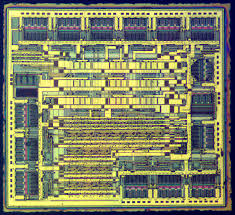

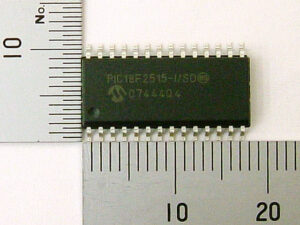

Microprocessor PIC18F2515 heximal file recovery is a process starts from unlock protective PIC18F2515 microchip MCU fuse bit and read embedded firmware out in the format of binary code and heximal data from secured microcontroller PIC18F2515;

microprocessor PIC18F2515 heximal file recovery is a process starts from unlock protective PIC18F2515 microchip MCU fuse bit and read embedded firmware out in the format of binary code and heximal data from secured microcontroller PIC18F2515;

Using the internal oscillator as the clock source when Crack MCU Flash eliminates the need for up to two external oscillator pins which will provide great benefit for Microprocessor PIC18F2515 Heximal File Recovery and can then be used for digital I/O. Two distinct configurations are available:

- In INTIO1 mode, the OSC2 pin outputs FOSC/4, while OSC1 functions as RA7 for digital input and output.

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6, both for digital input and output.

Odzyskiwanie pliku heksadecymalnego mikroprocesora PIC18F2515 to proces rozpoczynający się od odblokowania zabezpieczającego bitu bezpiecznika mikroprocesora PIC18F2515 i odczytania wbudowanego oprogramowania sprzętowego w formacie kodu binarnego i danych heksadecymalnych z zabezpieczonego mikrokontrolera PIC18F2515;

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8.0 MHz through the process of Restore Microprocessor Program Most Important Two Steps. The INTRC oscillator operates independently of the INTOSC source. Any changes in INTOSC across voltage and temperature are not necessarily reflected by changes in INTRC and vice versa.

The internal oscillator’s output has been calibrated at the factory but can be adjusted in the user’s application. This is done by writing to the OSCTUNE register (Register 2-1).

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. The INTOSC clock will stabilize within 1 ms by Break Atmel AVR MCU ATmega8535L Heximal. Code execution continues during this shift. There is no indication that the shift has occurred.

The OSCTUNE register also implements the INTSRC and PLLEN bits, which control certain features of the internal oscillator block. The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected for the purpose of Microprocessor PIC18F2515 Heximal File Recovery. This is covered in greater detail in Section 2.7.1 “Oscillator Control Register”.

mikroişlemci PIC18F2515 heksimal dosya kurtarma işlemi, koruyucu PIC18F2515 mikroçip MCU sigorta bitinin kilidini açmak ve güvenli mikrodenetleyici PIC18F2515’ten ikili kod ve heksimal veri biçiminde gömülü aygıt yazılımını okumakla başlayan bir işlemdir;

The PLLEN bit controls the operation of the frequency multiplier, PLL, in Internal Oscillator modes after Recover Atmel AVR Controller ATmega48V Firmware.

The 4x frequency multiplier can be used with the internal oscillator block to produce faster device clock speeds than are normally possible with an internal oscillator. When enabled, the PLL produces a clock speed of up to 32 MHz. Unlike HSPLL mode, the PLL is controlled through software. The control bit, PLLEN (OSCTUNE<6>), is used to enable or disable its operation by Break IC ATmega88V Internal Flash.

The PLL is available for use with the INTOSC when:

- The primary clock is the INTOSC clock source (selected in CONFIG1H<3:0>), and

- The 4 or 8 MHz INTOSC output is selected.

Writes to the PLLEN bit will be ignored until both these conditions are met.