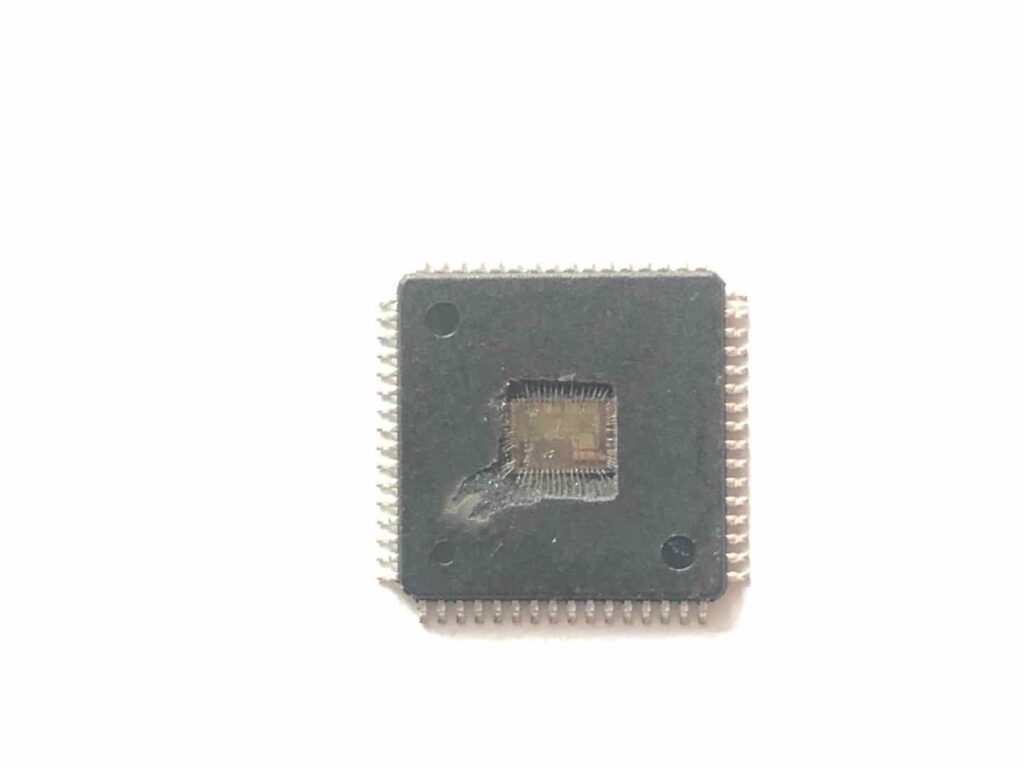

Clone STMicroelectronics SPC56EL54L5 Microcontroller Memory Heximal

Clone STMicroelectronics SPC56EL54L5 Microcontroller Memory Heximal

Clone STMicroelectronics SPC56EL54L5 Microcontroller Memory Heximal from its secured flash memory, the extracted program can be rewritten to new MCU SPC56EL54L5 which can provide the same functions as original MCU, master microcontroller status will be decrypted from locked to unlocked one;

This device includes programmable, non-volatile flash memory. The non-volatile memory (NVM) can be used for instruction storage or data storage, or both. The flash memory module interfaces with the system bus through a dedicated flash memory array controller.

It supports a 64-bit data bus width at the system bus port, and a 128-bit read data interface to flash memory. The module contains four 128-bit prefetch buffers. Prefetch buffer hits allow no-wait responses. Buffer misses incur a 3 wait state response at 120 MHz as the consequence of copying freescale microprocessor spc564l70l3 memory binary.

The flash memory module provides the following features:

- 2 MB of flash memory in unique multi-partitioned hard macro

- Sectorization:

- Partition 1 (low address): 16 KB + 16 KB + 16 KB + 16 KB

- Partition 2 (low address): 16 KB + 16 KB + 16 KB + 16 KB

- Partition 3 (low address): 64 KB + 64 KB

- Partition 4 (mid address): 128 KB + 128 KB

- Partition 5 (high address): 256 KB + 256 KB

- Partition 6 (high address): 256 KB + 256 KB

- Partition 7 (high address): 256 KB + 256 KB

- EEPROM emulation (in software) within same module but on different partition

- 16 KB test sector and 16 KB shadow sector for test, censorship device and user option bits

- Wait states:

- Access time less or equal to 3 WS at 120 MHz + 4% FM (4-1-2-1 access)

- Access time less or equal to 2 WS at 80 MHz + 4% FM

- Flash memory line 128-bit wide with 8-bit ECC on 64-bit word (total 144 bits)

- Accessed via a 64-bit wide bus for write and a 128-bit wide array for read operations

- 1-bit error correction, 2-bit error detection

- Sectorization:

The SPC56XL70 SRAM provides a general-purpose single port memory

ECC handling is done on a 32-bit boundary for data and it is extended to the address to have the highest possible diagnostic coverage including the array internal address decoder and cloning spc564l70l5 mcu flash memory firmware.

The SRAM module provides the following features:

- System SRAM: 192 KB

- ECC on 32-bit word (syndrome of 7 bits)

- ECC covers SRAM bus address

- 1-bit error correction, 2-bit error detection

- Wait states:

- 1 wait state at 120 MHz

- 0 wait states at 80 MHz

- ECC on 32-bit word (syndrome of 7 bits)