Archive for the ‘Reverse Engineer Microcontroller’ Category

Reverse Engineering Microcontroller PIC16F747 Code

Reverse Engineering Microcontroller PIC16F747 Code

We can Reverse engineering Microcontroller PIC16F747 Code, please view the Microcontroller PIC16F747 features for your reference:

Special Microcontroller Features:

· Fail-Safe Clock Monitor for protecting critical applications against crystal failure when Reverse engineering Microcontroller code;

· Two-Speed Start-up mode for immediate code execution

· Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Programmable Code Protection can be used also for Break Microcontroller PIC18F4220 Binary

· Processor Read Access to Program Memory

· Power-Saving Sleep mode

· In-Circuit Serial Programming (ICSP) via two pins

· MPLAB® In-Circuit Debug (ICD) via two pins

· MCLR pin function replaceable with input only pin

DEVICE OVERVIEW

This document contains device specific information about the following devices:

PIC16F737/767 devices are available only in 28-pin packages, while PIC16F747 devices are available in 40-pin and 44-pin packages. All devices in the PIC16F7X7 family share common architecture with the following differences:

· The PIC16F737 and PIC16F767 have one-half of the total on-chip memory of the PIC16F747 and PIC16F777.

· The 28-pin devices have 3 I/O ports, while the 40/44-pin devices have 5.

· The 28-pin devices have 16 interrupts, while the 40/44-pin devices have 17.

· The 28-pin devices have 11 A/D input channels, while the 40/44-pin devices have 14.

· The Parallel Slave Port is implemented only on the 40/44-pin devices.

· Low-Power modes: RC_RUN allows the core and peripherals to be clocked from the INTRC, while SEC_RUN allows the core and peripherals to be clocked from the low-power Timer1. Refer to Section 4.7 “Power-Managed Modes” for further details for the purpose of Reverse engineering Microcontroller code.

· Internal RC oscillator with eight selectable frequencies, including 31.25 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz and 8 MHz. The INTRC can be configured as a primary or secondary clock source when Crack MCU. Refer to Section 4.5 “Internal Oscillator Block” for further details.

Copy Microcontroller PIC16F737 Flash

Copy Microcontroller PIC16F737 Flash

Copy Microcontroller PIC16F737 Flash

Copy Microcontroller PIC16F737 Flash starts from knowing its basic features, below we will introduce it:

Low-Power Features:

· Power-Managed modes:

– Primary Run (XT, RC oscillator, 76 µA, 1 MHz, 2V)

– RC_RUN (7 µA, 31.25 kHz, 2V)

– SEC_RUN (9 µA, 32 kHz, 2V)

– Sleep (0.1 µA, 2V)

· Timer1 Oscillator (1.8 µA, 32 kHz, 2V)

· Watchdog Timer (0.7 µA, 2V)

· Two-Speed Oscillator Start-up Oscillators:

· Three Crystal modes:

– LP, XT, HS (up to 20 MHz)

· Two External RC modes

– ECIO (up to 20 MHz)

· Internal Oscillator Block:

– 8 user-selectable frequencies (31 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz, 8 MHz) after Copy Microcontroller

Analog Features:

· 10-bit, up to 14-channel Analog-to-Digital Converter:

– Programmable Acquisition Time

– Conversion available during Sleep mode

· Dual Analog Comparators

· Programmable Low-Current Brown-out Reset (BOR) Circuitry and Programmable Low-Voltage Detect (LVD) A, 32 kHz, 2V) if Unlock Microcontroller

– Sleep (0.1 µA, 2V)

· Timer1 Oscillator (1.8 µA, 32 kHz, 2V)

· Watchdog Timer (0.7 µA, 2V)

· Two-Speed Oscillator Start-up Oscillators:

· Three Crystal modes:

– LP, XT, HS (up to 20 MHz)

· Two External RC modes

– ECIO (up to 20 MHz)

· Internal Oscillator Block:

– 8 user-selectable frequencies (31 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz, 8 MHz).

Copy Microcontroller PIC16CR83 Heximal

Copy Microcontroller PIC16CR83 Heximal

Copy Microcontroller PIC16CR83 Heximal

A variety of frequency ranges and packaging options are available in the process of Copy Microcontroller PIC16CR83 Heximal. Depending on application and production requirements the proper device option can be selected using the information in this section. When placing orders, please use the “PIC16F8X Product Identification System” at the back of this data sheet to specify the correct part number.

There are four device “types” as indicated in the device number.

1. F, as in PIC16F84. These devices have Flash program memory and operate over the standard voltage range.

2. LF, as in PIC16LF84. These devices have Flash;

LCR, as in PIC16LCR84. These devices have ROM program memory and operate over an extended voltage range.

When discussing memory maps and other architectural features, the use of F and CR also implies the LF and LCR versions.

These devices are offered in the lower cost plastic package, even though the device can be erased and reprogrammed. This allows the same device to be used for prototype development and pilot programs as well as production.

A further advantage of the electrically-erasable Flash version is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip’s PICSTART® Plus or PRO MATE® II programmers.

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices have all Flash locations and configuration options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available from Copy Microcontroller PIC16CR83 Heximal.

For information on submitting a QTP code, please contact your Microchip Regional Sales Office.

Microchip offers the unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.device where the program memory is a ROM. These Some of Microchip’s devices have a corresponding devices give a cost savings over Microchip’s traditional user programmed devices (EPROM, EEPROM). ROM devices (PIC16CR8X) do not allow serialization information in the program memory space. The user may program this information into the Data EEPROM.

Copy Microcontroller PIC16F887 File

Copy Microcontroller PIC16F887 File

Copy Microcontroller PIC16F887 File

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register when Copy Microcontroller PIC16F887 File.

Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0×00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, “Implementing a Table Read” (DS00556)

There are as many as thirty-five general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 3-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input enabled, the associated pin may not be used as a general purpose I/O pin. output driver).

Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 3-1 shows how to initialize PORTA.

Reading the PORTA register (Register 3-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write address rolls over from 0xFF to 0×00 in the middle of operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch from Copy Microcontroller PIC16F887 File.

The TRISA register (Register 3-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read “0″.

Additional Pin Functions

RA0 also has an Ultra Low-Power Wake-up option. The next three sections describe these functions.

The ANSEL register (Register 3-3) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSEL bit high will cause all digital reads on the pin to be read as ‘0’ and allow analog functions on the pin to operate correctly.

The state of the ANSEL bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

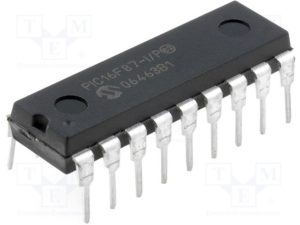

Copy Chip PIC16F87 Code

Copy Chip PIC16F87 Code

Copy Chip PIC16F87 Code

Copy Chip PIC16F87 Code from the memory which include flash and eeprom, then the program will be rewrite to other blank PIC16F87 which will perform the same functions as original PIC16F87 microcontroller:

Low-Power Features:

· Power Managed modes:

Copy Chip PIC16F87 Code

– Primary RUN: RC oscillator, 76 µA, 1 MHz, 2V

– RC_RUN: 7 µA, 31.25 kHz, 2V

– SEC_RUN: 9 µA, 32 kHz, 2V

– SLEEP: 0.1 µA, 2V

· Timer1 Oscillator: 1.8 µA, 32 kHz, 2V

· Watchdog Timer: 2.2 µA, 2V

· Two-Speed Oscillator Start-up Oscillators:

· Three Crystal modes:

– LP, XT, HS: up to 20 MHz

· Two External RC modes

– ECIO: up to 20 MHz

· Internal oscillator block:

– 8 user selectable frequencies: 31 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz, 8 MHz

Peripheral Features:

· Capture, Compare, PWM (CCP) module:

– Capture is 16-bit, max. resolution is 12.5 ns

– Compare is 16-bit, max. resolution is 200 ns

– PWM max. resolution is 10-bit

· 10-bit, 7-channel Analog-to-Digital Converter

· Synchronous Serial Port (SSP) with SPI™ (Master/Slave) and I2C™ (Slave)

· Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI) with 9-bit address detection:

– RS-232 operation using internal oscillator (no external crystal required)

· Dual Analog Comparator module:

– Programmable on-chip voltage reference

– Programmable input multiplexing from device inputs and internal voltage reference

– Comparator outputs are externally accessible

Special Microcontroller Features:

· 100,000 erase/write cycles Enhanced FLASH program memory typical

· 1,000,000 typical erase/write cycles EEPROM data memory typical

· EEPROM Data Retention: > 40 years

· In-Circuit Serial Programming™ (ICSP™) – via two pins

· Processor read/write access to program memory

· Low-Voltage Programming

· In-Circuit Debugging via two pins

· Extended Watchdog Timer (WDT):

– Programmable period from 1 ms to 268s

· Wide operating voltage range: 2.0V to 5.5V

Copy Microcontroller PIC16F677 Code

Copy Microcontroller PIC16F677 Code

We can Copy Microcontroller PIC16F677 Code, please view the Microcontroller PIC16F677 features for your reference:

Low-Power Features:

· Standby Current:

– 50 nA @ 2.0V, typical

· Operating Current:

– 11 ìA @ 32 kHz, 2.0V, typical

– 220 ìA @ 4 MHz, 2.0V, typical

· Watchdog Timer Current:

– <1 ìA @ 2.0V, typical

Peripheral Features:

· 17 I/O pins and 1 input only pin:

– High current source/sink for direct LED drive

– Interrupt-on-Change pin

– Individually programmable weak pull-ups

– Ultra Low-Power Wake-up (ULPWU)

· Analog Comparator module with:

– Two analog comparators

– Programmable on-chip voltage reference (CVREF) module (% of VDD)

– Comparator inputs and outputs externally accessible

– Timer 1 Gate Sync Latch

– Fixed 0.6V VREF

· A/D Converter:

– 10-bit resolution and 12 channels

· Timer0: 8-bit timer/counter with 8-bit programmable prescaler

· Enhanced Timer1:

– 16-bit timer/counter with prescaler

– External Timer1 Gate (count enable)

– Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Enhanced Capture, Compare, PWM+ module:

– 16-bit Capture, max resolution 12.5 ns

– Compare, max resolution 200 ns

– 10-bit PWM with 1, 2 or 4 output channels, programmable “dead time”, max frequency 20 kHz

– PWM output steering control

· Synchronous Serial Port (SSP):

– SPI mode (Master and Slave)

· I2C™ (Master/Slave modes):

– I2C™ address mask

· In-Circuit Serial ProgrammingTM (ICSPTM) via two pins

Circuit Engineering Company Limited continues to be recognized as the Southern China Leader in Services for Microcontroller REVERSE ENGINEERING. With the advancement of today’s modern circuit board technology, it is more important than ever to have specialists available to help you at a moment’s notice. Our engineering and commercial teams collectively have a vast amount of electronic experience covering field include Consumer Electronics, Industrial Automation Electronics, Wireless Communication Electronics., etc. For more information please contact us through email.

Copy Microcontroller PIC16F627A Binary

Copy Microcontroller PIC16F627A Binary

We can Copy Microcontroller PIC16F627A Binary, please view the Microcontroller PIC16F627A features for your reference:

High Performance RISC CPU:

Operating speeds from DC – 20 MHz

Interrupt capability

Direct, Indirect and Relative Addressing modes

35 single word instructions

– All instructions single cycle except branches

Special Microcontroller Features:

· Internal and external oscillator options

– Precision Internal 4 MHz oscillator factory calibrated to ±1%

– Low Power Internal 37 kHz oscillator

– External Oscillator support for crystals and resonators

· Power saving SLEEP mode

· Programmable weak pull-ups on PORTB

· Multiplexed Master Clear/Input-pin

· Watchdog Timer with independent oscillator for reliable operation

· Low voltage programming

· In-Circuit Serial Programming™ (via two pins)

· Programmable code protection

· Brown-out Reset

· Power-on Reset

· Power-up Timer and Oscillator Start-up Timer

· Wide operating voltage range. (2.0 – 5.5V)

· Industrial and extended temperature range

· High Endurance FLASH/EEPROM Cell

– 100,000 write FLASH endurance

– 1,000,000 write EEPROM endurance

Low Power Features:

· Standby Current:

– 100 nA @ 2.0V, typical

· Operating Current:

– 12 µA @ 32 kHz, 2.0V, typical

– 120 µA @ 1 MHz, 2.0V, typical

· Watchdog Timer Current

– 1 µA @ 2.0V, typical

· Timer1 oscillator current:

– 1.2 µA @ 32 kHz, 2.0V, typical

· Dual Speed Internal Oscillator:

– Run-time selectable between 4 MHz and 37 kHz

– 4 µs wake-up from SLEEP, 3.0V, typical

Peripheral Features:

· 16 I/O pins with individual direction control

· High current sink/source for direct LED drive

· Analog comparator module with:

– Two analog comparators

– Programmable on-chip voltage reference (VREF) module

– Selectable internal or external reference

– Comparator outputs are externally accessible

· Timer0: 8-bit timer/counter with 8-bit programmable prescaler

· Timer1: 16-bit timer/counter with external crystal/clock capability

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Capture, Compare, PWM module

– 16-bit Capture/Compare

– 10-bit PWM

· Addressable Universal Synchronous/Asynchronous Receiver/Transmitter USART/SCI

Copy IC PIC16F884 Code

Copy IC PIC16F884 Code

Copy IC PIC16F884 Code is covered by this data sheet. The PIC16F884 is available in 28-pin PDIP, SOIC, SSOP and QFN packages. The PIC16F884/887 is available in a 40-pin PDIP and 44-pin QFN and TQFP packages when Copy IC. Figure 1-1 shows the block diagram of PIC16F884 and Figure 1-2 shows a block diagram of the PIC16F884 device.

Table 1-1 and Table 1-2 show the corresponding pinout descriptions. The PIC16F884 has a 13-bit program counter capable of addressing a 2K x 14 (0000h-07FFh) for the PIC16F882, 4K x 14 (0000h-0FFFh) for the PIC16F883/PIC16F884, and 8K x 14 (0000h-1FFFh) for the PIC16F884 program memory space.

Accessing a location above these boundaries will cause a wrap-around within the first 8K x 14 space. The Reset vector is at 0000h and the interrupt vector is at 0004h.

Copy IC PIC16F884 Code

The data memory is partitioned into four banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. The General Purpose Registers, implemented as static RAM, are located in the last 96 locations of each Bank.

Register locations F0h-FFh in Bank 1, 170h-17Fh in Bank 2 and 1F0h-1FFh in Bank 3, point to addresses 70h-7Fh in Bank 0. The actual number of General Purpose Resisters (GPR) implemented in each Bank depends on the device when Copy IC PIC16F884 Code. Details are shown in Figures 2-5 and 2-6. All other RAM is unimplemented and returns ‘0’ when read. RP<1:0> of the STATUS register are the bank select bits:

RP1 RP0

→Bank 0 is selected

→Bank 1 is selected

→Bank 2 is selected

→Bank 3 is selected

Circuit Engineering Company Limited continues to be recognized as the Southern China Leader in Services for IC Read, MCU Crack, Chip Copy, Microcontroller Unlock service. With the advancement of today’s modern circuit board technology, it is more important than ever to have specialists available to help you at a moment’s notice. Our engineering and commercial teams collectively have a vast amount of electronic experience covering field include Consumer Electronics, Industrial Automation Electronics, Wireless Communication Electronics., etc. For more information please contact us through email.

Copy Microcontroller PIC18F4515 Code

Copy Microcontroller PIC18F4515 Code

Like previous PIC18 devices, Copy Microcontroller PIC18F4515 Code includes a feature that allows the device clock source to be switched from the main oscillator to an alternate low-frequency clock source. PIC18F2X1X/4X1X devices offer two alternate clock sources.

When an alternate clock source is enabled, the various power managed operating modes are available. Essentially, there are three clock sources for these devices:

· Primary oscillators

· Secondary oscillators

· Internal oscillator block

The primary oscillators include the External Crystal and Resonator modes, the External RC modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC3:FOSC0 configuration bits. The details of these modes are covered earlier in this chapter.

The secondary oscillators are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power managed mode. PIC18F2X1X/4X1X devices offer the Timer1 oscillator as a secondary oscillator which will bring more difficult in the process of Copy Microcontroller PIC18F4515 Code. This oscillator, in all power managed modes, is often the time base for functions such as a real-time clock.

Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T13CKI and RC1/T1OSI pins. Like the LP mode oscillator circuit, loading capacitors are also connected from each pin to ground. The Timer1 oscillator is discussed in greater detail in Section 11.3 “Timer1 Oscillator”.

In addition to being a primary clock source, the internal oscillator block is available as a power managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

The clock sources for the PIC18F2X1X/4X1X devices are shown in Figure 2-8. See Section 22.0 “Special Features of the CPU” for Configuration register details. The OSCCON register (Register 2-2) controls several aspects of the device clock’s operation, both in full power operation and in power managed modes.

The System Clock Select bits, SCS1:SCS0, select the clock source. The available clock sources are the primary clock (defined by the FOSC3:FOSC0 configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval.

Copy IC PIC12C671 Eeprom

Copy IC PIC12C671 Eeprom

We can Copy IC PIC12C671 Eeprom, please view the IC PIC12C671 features for your reference:

High-Performance RISC CPU:

· Only 35 single word instructions to learn

· All instructions are single cycle (400 ns) except for program branches which are two-cycle

· Operating speed: DC – 10 MHz clock input DC – 400 ns instruction cycle

· 14-bit wide instructions 8-bit wide data path

· Interrupt capability

· Special function hardware registers

· 8-level deep hardware stack

· Direct, indirect and relative addressing modes for data and instructions

Peripheral Features:

· Four-channel, 8-bit A/D converter

· 8-bit real time clock/counter (TMR0) with 8-bit programmable prescaler

· 1,000,000 erase/write cycle EEPROM data memory

· EEPROM data retention > 40 years

Special Microcontroller Features:

In-Circuit Serial Programming (ICSP™)

Internal 4 MHz oscillator with programmable calibration

Selectable clockout

Power-on Reset (POR)

Power-up Timer (PWRT) and Oscillator Start-up

Timer (OST)

Copy IC PIC12C671 Eeprom

Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation and facilitate the operation of Copy IC PIC12C671 Eeprom

Power saving SLEEP mode

Interrupt-on-pin change (GP0, GP1, GP3)

Internal pull-ups on I/O pins (GP0, GP1, GP3)

Internal pull-up on MCLR pin

Selectable oscillator options:

– INTRC: Precision internal 4 MHz oscillator

– EXTRC: External low-cost RC oscillator

– XT: Standard crystal/resonator

– HS: High speed crystal/resonator

– LP: Power saving, low frequency crystal

CMOS Technology:

· Low-power, high-speed CMOS EPROM/EEPROM technology

· Fully static design

· Wide operating voltage range 2.5V to 5.5V

· Commercial, Industrial and Extended temperature ranges

· Low power consumption

< 2 mA @ 5V, 4 MHz

15 µA typical @ 3V, 32 kHz

< 1 µA typical standby current