Archive for the ‘Recover MCU’ Category

Attack MCU PIC12F675 Binary

Attack MCU PIC12F675 Binary

Attack MCU PIC12F675 Binary

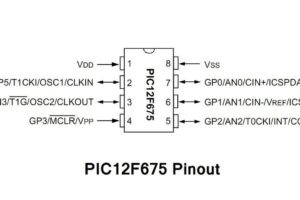

This document contains device specific information for the PIC12F675. Additional information may be found in the PIC® Mid-Range Reference Manual (DS33023) from Attack MCU PIC12F675 Binary, which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site.

The Reference Manual should be considered a complementary document to this Data Sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

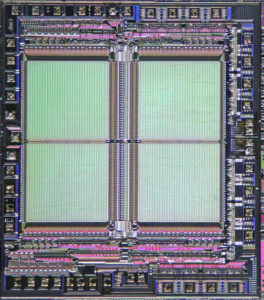

The PIC12F629 and PIC12F675 devices are covered by this Data Sheet. They are identical, except the PIC12F675 has a 10-bit A/D converter. They come in 8-pin PDIP, SOIC, MLF-S and DFN packages. Figure 1-1 shows a block diagram of the PIC12F675 devices. Below Table shows the pinout description.

The PIC12F675 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the PIC12F629/675 devices is physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space from UNLOCK MICROCONTROLLER.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose locations of each bank. Register locations 20h-5Fh are General Purpose Registers, implemented as static RAM and are mapped across both banks. All other RAM is unimplemented and returns ‘0’ when read. RP0 (STATUS<5>) is the bank select bit.

Registers and the Special Function Registers. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20h-5Fh are General Purpose Registers, implemented as static RAM and are mapped across both banks. All other RAM is unimplemented and returns ‘0’ when read. RP0 (STATUS<5>) is the bank select bit.

Attack PIC MCU 16F506 Code

Attack PIC MCU 16F506 Code

We can attack PIC MCU 16F506 Code, please view the PIC MCU features for your reference:

High-Performance RISC CPU:

· Only 33 single-word instructions to learn

· All single-cycle instructions except for program branches, which are two-cycle

· 12-bit wide instructions

· 2-level deep hardware stack

· Direct, Indirect and Relative Addressing modes for data and instructions

· 8-bit wide data path

· 10 Special Function Hardware registers (PIC12F510)

· 13 Special Function Hardware registers (PIC16F506)

· Operating speed:

– DC – 8 MHz Crystal Oscillator (PIC12F510)

– DC – 500 ns instruction cycle (PIC12F510)

– DC – 20 MHz Crystal Oscillator (PIC16F506)

– DC – 200 ns instruction cycle (PIC16F506)

Special Microcontroller Features:

· 4 or 8 MHz selectable precision internal oscillator:

– Factory calibrated to ±1% when attack PIC MCU

· In-Circuit Serial Programming™ (ICSP™)

· In-Circuit Debugging (ICD) support

· Power-on Reset (POR)

· Device Reset Timer (DRT):

– Short DRT (1.125 ms, typical) for INTOSC, EXTRC and EC

– DRT (18 ms, typical) for HS, XT and LP

· Watchdog Timer (WDT) with dedicated on-chip RC oscillator for reliable operation

· Programmable code protection

· Multiplexed MCLR input pin if attack PIC MCU

· Selectable internal weak pull-ups on I/O pins

· Power-Saving Sleep mode

· Wake-up from Sleep on pin change

· Wake-up from Sleep on comparator change

Selectable oscillator options:

– INTOSC: 4/8 MHz precision Internal oscillator

– EXTRC: External low-cost RC oscillator

– XT: Standard crystal/resonator

– LP: Power-saving, low-frequency crystal

– HS: High-speed crystal/resonator (PIC16F506 only)

– EC: High-speed external clock input (PIC16F506 only) after Attack PIC MCU 16F506 Code

· Analog-to-Digital (A/D) Converter:

– 8-bit resolution

– 4-input channels (1 channel is dedicated to conversion of the internal 0.6V absolute voltage reference)

· High current sink/source for direct LED drive

· 8-bit real-time clock/counter (TMR0) with 8-bit programmable prescaler

Low-Power Features/CMOS Technology:

· Operating Current:

– < 170 ìA @ 2V, 4 MHz

· Standby Current:

– 100 nA @ 2V, typical

· Low-power, high-speed Flash technology:

– 100,000 cycle Flash endurance for the purpose of recover MCU

– > 40-year retention

· Fully static design

· Wide operating voltage range: 2.0V to 5.5V

· Wide temperature range:

– Industrial: -40°C to +85°C

– Extended: -40°C to +125°C e:AR-SA’>programmable prescaler

Attack MCU PIC16C712 Binary

Attack MCU PIC16C712 Binary

We can Attack MCU PIC16C712 Binary, please view the MCU PIC16C712 features for your reference:

Microcontroller Core Features:

· High-performance RISC CPU

· Only 35 single word instructions to learn

· All single cycle instructions except for program branches which are two cycle when Attack MCU PIC16C712 Binary

· Operating speed: DC – 20 MHz clock input DC – 200 ns instruction cycle

· Interrupt capability (up to 7 internal/external interrupt sources)

· Eight level deep hardware stack

· Direct, indirect and relative addressing modes

· Power-on Reset (POR)

· Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

· Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

· Brown-out detection circuitry for Brown-out Reset (BOR)

· Programmable code-protection

· Power saving SLEEP mode

· Selectable oscillator options

· Low-power, high-speed CMOS EPROM technology

· Fully static design

· In-Circuit Serial Programming (ICSP) after Attack MCU PIC16C712 Binary

· Wide operating voltage range: 2.5V to 5.5V

· High Sink/Source Current 25/25 mA

· Commercial, Industrial and Extended temperature ranges

· Low-power consumption:

– < 2 mA @ 5V, 4 MHz

– 22.5 µA typical @ 3V, 32 kHz

– < 1 µA typical standby current

Peripheral Features:

· Timer0: 8-bit timer/counter with 8-bit prescaler

· Timer1: 16-bit timer/counter with prescaler can be incremented during sleep via external crystal/clock

· Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

· Capture, Compare, PWM module

· Capture is 16-bit, max. resolution is 12.5 ns, Compare is 16-bit, max. resolution is 200 ns, PWM maximum resolution is 10-bit

· 8-bit multi-channel Analog-to-Digital converter

This document contains device-specific information. Additional information may be found in the PICmicro™ Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website when Attack MCU. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules before Attack MCU PIC16C712 Binary.

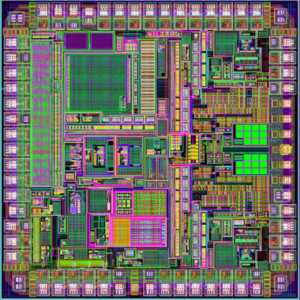

There are two devices (PIC16C712, PIC16C716) covered by this datasheet. Figure 1-1 is the block diagram for both devices. The pinouts are listed in Table 1-1.

Attack IC PIC16F57 Program

Attack IC PIC16F57 Program

Attack IC PIC16F57 Program

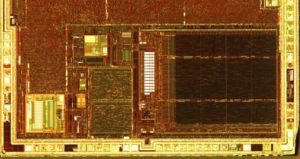

The PIC16F5X from Microchip Technology is a family of low-cost, high-performance, 8-bit, fully static, Flash based CMOS microcontrollers. It employs a RISC architecture with only 33 single-word/single-cycle instructions. All instructions are single cycle except for program branches which take two cycles by Attack IC PIC16F57 Program. The PIC16F5X delivers performance an order of magnitude higher than its competitors in the same price category.

The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy-to-use and easy-to-remember instruction set reduces development time significantly.

The PIC16F5X products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external Reset circuitry.

There are four oscillator configurations to choose from, including the power-saving LP (Low Power) oscillator and cost saving RC oscillator. Power-saving Sleep mode, Watchdog Timer and code protection features improve system cost, power and reliability.

The PIC16F5X products are supported by a full-featured macro assembler, a software simulator, a low-cost development programmer and a full featured programmer. All the tools are supported on IBM® PC and compatible machines.

The PIC16F5X series fits perfectly in applications ranging from high-speed automotive and appliance motor control to low-power remote transmitters/receivers, pointing devices and telecom processors. The Flash technology makes customizing application programs from Attack IC PIC16F57 Program (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient.

The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC16F5X series very versatile, even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of “glue” logic in larger systems, co-processor applications).

Attack MCU PIC16C715 Software

Attack MCU PIC16C715 Software

Attack MCU PIC16C715 Software

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance input mode when Attack MCU PIC16C715 Software. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB’s pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison).

The input pins (of RB7:RB4) are compared with the old value latched on the last attack of PORTB. The “mismatch” outputs of RB7:RB4 are OR’ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

Any instruction which writes, operates internally as a attack followed by a write operation. The BCF and BSF instructions, for example, attack the register into the CPU, execute the bit operation and write the result back to the register to ease the process of Attack MCU PIC16C715 Software. Caution must be used when these instructions are applied to a port with both inputs and outputs defined.

For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be attack into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches.

If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be attack into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched to an output, the content of the data latch may now be unknown.

The actual write to an I/O port happens at the end of an instruction cycle, whereas for attacking, the data must be valid at the beginning of the instruction cycle. Therefore, care must be exercised if a write followed by a attack operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be attack into the CPU is executed.

Otherwise, the previous state of that pin may be attack into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

Attack Chip PIC16C73A Program

Attack Chip PIC16C73A Program

The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I2C) bus which can be used to Attack Chip PIC16C73A Program.

The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI. Also a 5-channel high-speed 8-bit A/D is provided.The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C73A devices have 192 bytes of RAM, while the PIC16C73A has 368 bytes of RAM. Each device has 33 I/O pins. In addition several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports.

The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I2C) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI.

Attack Chip PIC16C73A Program

An 8-bit Parallel Slave Port is provided. Also an 8-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C7X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption.

There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets to Attack Chip PIC16C73A Program.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up. A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C7X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient.

The small footprint packages make this microcontroller series perfect for all applications with space limitations when Attack Chip. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C7X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

Attack IC PIC16C74B Binary

Attack IC PIC16C74B Binary

Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C74B Product Identification System section at the end of this data sheet which can help to ease the process of Attack IC PIC16C74B Binary.

For the PIC16C7X family, there are two device “types” as indicated in the device number:

1. C, as in PIC16C74. These devices have EPROM type memory and operate over the standard voltage range.

2. LC, as in PIC16LC74. These devices have EPROM type memory and operate over an extended voltage range.

The UV erasable version, offered in windowed CERDIP packages, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes. The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

Attack IC PIC16C74B Binary

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized to prohibit the operation of Attack IC PIC16C74B Binary. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory.

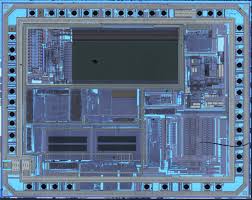

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which program and data are accessed from separate memories using separate buses.

This improves bandwidth over traditional von Neumann architecture, in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide, making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle.

A two-stage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, most instructions execute in a single cycle (200 ns @ 20 MHz) except for program branches. All devices covered by this data sheet contain 4K x 14-bit program memory and 192 x 8-bit data memory.

Attack CPLD EPM7096QC100-10 Binary

Attack CPLD EPM7096QC100-10 Binary

We can Attack CPLD EPM7096QC100-10 Binary, please view CPLD EPM7096QC100-10 features for your reference:

High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices

– ISP circuitry compatible with IEEE Std. 1532

Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells

Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2) 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect) PCI-compliant devices available.

Open-drain output option in MAX 7000S devices

Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

Programmable power-saving mode for a reduction of over 50% in each macrocell.

Configurable expander product-term distribution, allowing up to 32 product terms per macrocell 44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages.

Programmable security bit for protection of proprietary designs

– MultiVoltTM I/O interface operation, allowing devices to interface with 3.3-V or 5.0-V devices (MultiVolt I/O operation is not available in 44-pin packages) – Pin compatible with low-voltage MAX 7000A and MAX 7000B devices.

Enhanced features available in MAX 7000E and MAX 7000S devices

– Six pin- or logic-driven output enable signals

– Two global clock signals with optional inversion

– Enhanced interconnect resources for improved routability

– Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

Attack CPLD EPM7096QC100-10 Binary

– Programmable output slew-rate control

Software design support and automatic place-and-route provided by

Altera’s development system for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations

Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, and VeriBest Programming support.

– Altera’s Master Programming Unit (MPU) and programming hardware from third-party manufacturers program all MAX 7000 devices

– The BitBlasterTM serial download cable, ByteBlasterMVTM parallel port download cable, and MasterBlasterTM serial/universal serial bus (USB) download cable program MAX 7000S devices.

Attack PLD EPM7128ELC84-10 Binary

Attack PLD EPM7128ELC84-10 Binary

High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 which has provide convenience for Attack PLD EPM7128ELC84-10 Binary.

Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells

Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2) 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect)

Attack PLD EPM7128ELC84-10 Binary

PCI-compliant devices available

Open-drain output option in MAX 7000S devices

Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

Programmable power-saving mode for a reduction of over 50% in each macrocell

Configurable expander product-term distribution, allowing up to 32 product terms per macrocell

44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages

Programmable security bit for protection of proprietary designs

3.3-V or 5.0-V operation

– MultiVoltTM I/O interface operation, allowing devices to interface with 3.3-V or 5.0-V devices after Attack PLD EPM7128ELC84-10 Binary (MultiVolt I/O operation is not available in 44-pin packages)

– Pin compatible with low-voltage MAX 7000A and MAX 7000B devices

Enhanced features available in MAX 7000E and MAX 7000S devices

– Six pin- or logic-driven output enable signals

– Two global clock signals with optional inversion

– Enhanced interconnect resources for improved routability

– Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

– Programmable output slew-rate control

Software design support and automatic place-and-route provided by Altera’s development system for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations.

Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, and VeriBest.

Programming support

– Altera’s Master Programming Unit (MPU) and programming hardware from third-party manufacturers program all MAX 7000 devices

– The BitBlasterTM serial download cable, ByteBlasterMVTM parallel port download cable, and MasterBlasterTM serial/universal serial bus (USB) download cable program MAX 7000S devices

Attack AVR ATmega64L Program

Attack AVR ATmega64L Program

We can Attack AVR ATmega64L Program, please view below AVR ATMEGA64L features for your reference:

High-performance, Low-power Atmel® AVR® 8-bit Microcontroller

· Advanced RISC Architecture

– 130 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers + Peripheral Control Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-chip 2-cycle Multiplier

High Endurance Non-volatile Memory segments

– 64 Kbytes of In-System Reprogrammable Flash program memory

– 2 Kbytes EEPROM

– 4 Kbytes Internal SRAM

– Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85°C/100 years at 25°C(1)

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– Up to 64 Kbytes Optional External Memory Space

– Programming Lock for Software Security

– SPI Interface for In-System Programming

JTAG (IEEE std. 1149.1 Compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

– Two Expanded 16-bit Timer/Counters with Separate Prescaler, Compare Mode, and Capture Mode

– Real Time Counter with Separate Oscillator

– Two 8-bit PWM Channels

– 6 PWM Channels with Programmable Resolution from 1 to 16 Bits

– 8-channel, 10-bit ADC

8 Single-ended Channels

7 Differential Channels

2 Differential Channels with Programmable Gain (1x, 10x, 200x)

– Byte-oriented Two-wire Serial Interface

– Dual Programmable Serial USARTs

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with On-chip Oscillator before Attack AVR

– On-chip Analog Comparator

Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

– Software Selectable Clock Frequency

– ATmega103 Compatibility Mode Selected by a Fuse

– Global Pull-up Disable

I/O and Packages

– 53 Programmable I/O Lines

– 64-lead TQFP and 64-pad QFN/MLF

Operating Voltages

– 2.7V – 5.5V for ATmega64L

– 4.5V – 5.5V for ATmega64

Speed Grades

– 0 – 8 MHz for ATmega64L

– 0 – 16 MHz for ATmega64