Archive for the ‘Recover MCU’ Category

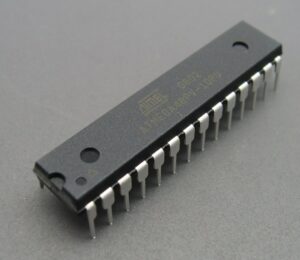

Reverse Engineering MCU ATMEGA48P Program

Reverse Engineering MCU ATMEGA48P Program

Reverse Engineering MCU ATMEGA48P Program from flash memory and copy heximal program to new microcontroller atmega48p secured chipset;

Not all 16-bit accesses uses the Temporary Register for the high byte. Reading the OCRnA/B/C 16-bit registers does not involve using the Temporary Register, To do a 16-bit write, the high byte must be written before the low byte. For a 16-bit read, the low byte must be read before the high byte.

The following code examples show how to access the 16-bit timer registers assuming that no interrupts updates the temporary register. The same principle can be used directly for accessing the OCRnA/B/C and ICRn Registers. Note that when using “C”, the compiler handles the 16-bit access.

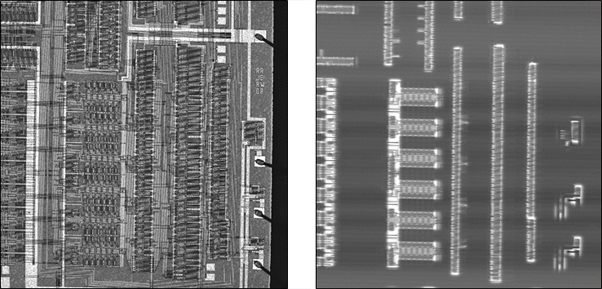

unlock encrypted atmega48pv microcontroller protective system and dump embedded heximal file from flash memory

The assembly code example returns the TCNTn value in the r17:r16 register pair. It is important to notice that accessing 16-bit registers are atomic operations when breaking microcontroller atmega48p atmel avr chip fuse bit. If an interrupt occurs between the two instructions accessing the 16-bit register, and the interrupt code updates the temporary register by accessing the same or any other of the 16-bit Timer Registers, then the result of the access outside the interrupt will be corrupted.

Therefore, when both the main code and the interrupt code update the temporary register, the main code must disable the interrupts during the 16-bit access after readout microcontroller atmega48pa binary file and heximal from eeprom and flash memory. The following code examples show how to do an atomic read of the TCNTn Register contents. Reading any of the OCRnA/B/C or ICRn Registers can be done by using the same principle.

If writing to more than one 16-bit register where the high byte is the same for all registers written, then the high byte only needs to be written once. However, note that the same rule of atomic operation described previously also applies in this case.

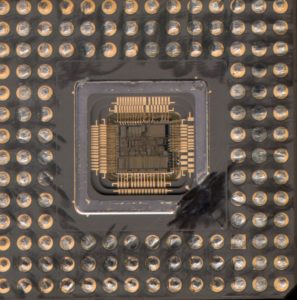

Recover Chip ATmega128PV Flash

Recover Chip ATmega128PV Flash

We can Recover CHIP ATMEGA128PV Flash, please view the CHIP ATMEGA128PV features for your reference:

The simplest mode of operation is the Normal mode (WGMn3:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed.

The counter simply overruns when it passes its maximum 16-bit value (MAX = 0xFFFF) and then restarts from the BOTTOM (0x0000).

In normal operation the Timer/Counter Over-flow Flag (TOVn) will be set in the same timer clock cycle as the TCNTn becomes zero.

The TOVn Flag in this case behaves like a 17th bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOVn Flag, the timer resolution can be increased by software.

There are no special cases to consider in the Normal mode, a new counter value can be written anytime. The Input Capture unit is easy to use in Normal mode. However, observe that the maximum interval between the external events must not exceed the resolution of the counter.

If the interval between events are too long, the timer overflow interrupt or the prescaler must be used to extend the resolution for the capture unit. The Output Compare units can be used to generate interrupts at some given time.

Using the Output Compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time. In Clear Timer on Compare or CTC mode (WGMn3:0 = 4 or 12), the OCRnA or ICRn Register are used to manipulate the counter resolution.

In CTC mode the counter is cleared to zero when the counter value (TCNTn) matches either the OCRnA (WGMn3:0 = 4) or the ICRn (WGMn3:0 = 12). The OCRnA or ICRn define the top value for the counter, hence also its resolution.

This mode allows greater control of the compare match output frequency. It also simplifies the operation of counting external events. The timing diagram for the CTC mode is shown in Figure 54. The counter value (TCNTn) increases until a compare match occurs with either OCRnA or ICRn, and then counter (TCNTn) is cleared.

An interrupt can be generated at each time the counter value reaches the TOP value by either using the OCFnA or ICFn Flag according to the register used to define the TOP value. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing the TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature.

If the new value written to OCRnA or ICRn is lower than the current value of TCNTn, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFFFF) and wrap around starting at 0x0000 before the compare match can occur. In many cases this feature is not desirable. An alternative will then be to use the fast PWM mode using OCRnA for defining TOP (WGMn3:0 = 15) since the OCRnA then will be double buffered.

For generating a waveform output in CTC mode, the OCnA output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COMnA1:0 = 1). The OCnA value will not be visible on the port pin unless the data direction for the pin is set to output (DDR_OCnA = 1).

The waveform generated will have a maximum frequency of fOCnA = fclk_I/O/2 when OCRnA is set to zero (0x0000). The waveform frequency is defined by the following equation.

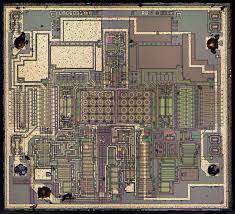

Recover Chip ATmega640P Heximal

Recover Chip ATmega640P Heximal

Recover Chip ATmega640P Heximal from Microcontroller ATmega640P flash and eeprom memory, rewrite the firmware to blank MCU ATmega640P by Microprocessor copying technique, unlock MCU secured system and reset the status of Microcontroller from locked to unlocked;

Recover Chip ATmega640P Heximal from Microcontroller ATmega640P flash and eeprom memory, rewrite the firmware to blank MCU ATmega640P by Microprocessor copying technique, unlock MCU secured system and reset the status of Microcontroller from locked to unlocked

In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC0x) bit. Forcing Compare Match will not set the OCF0x Flag or reload/clear the timer, but the OC0x pin will be updated as if a real Compare Match had occurred (the COM0x1:0 bits settings define whether the OC0x pin is set, cleared or toggled) if MCU PIC16F917 heximal breaking.

All CPU write operations to the TCNT0 Register will block any Compare Match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR0x to be initialized to the same value as TCNT0 without triggering an interrupt when the Timer/Counter clock is enabled.

Since writing TCNT0 in any mode of operation will block all Compare Matches for one timer clock cycle, there are risks involved when changing TCNT0 when using the Output Compare Unit, independently of whether the Timer/Counter is running or not after recover MCU PIC16F72 code.

If the value written to TCNT0 equals the OCR0x value, the Compare Match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is down-counting.

The setup of the OC0x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC0x value is to use the Force Output Compare (FOC0x) strobe bits in Normal mode if recover MCU PIC16F77 eeprom heximal.

The OC0x Registers keep their values even when changing between Waveform Generation modes. Be aware that the COM0x1:0 bits are not double buffered together with the compare value. Changing the COM0x1:0 bits will take effect immediately.

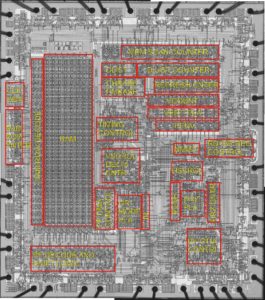

Attack MCU PIC16C558 Program

Attack MCU PIC16C558 Program

Attack MCU PIC16C558 secured system by disable the security fuse bit embedded in the microcontroller PIC16C558 , extract microprocessor program and data from flash memory;

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized when Attack MCU. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available after breaking MCU PIC10F200 program.

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential. The high performance of the PIC16C55X(A) family can be attributed to a number of architectural features commonly found in RISC microprocessors.

To begin with, the PIC16C55X(A) uses a Harvard architecture, in which, program and data are accessed from separate memories using separate busses after Attack MCU. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data words. Instruction opcodes are 14-bits wide making it possible to have all single word instructions.

A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

The PIC16C554(A) addresses 512 x 14 on-chip program memory. The PIC16C556A addresses 1K x 14 program memory. The PIC16C558(A) addresses 2K x 14 program memory. All program memory is internal. The PIC16C55X(A) can directly or indirectly address its register files or data memory when unlock microprocessor pic16c558 protective system and extract firmware from flash and eeprom memory.

All special function registers including the program counter are mapped into the data memory. The PIC16C55X(A) have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode after Attack MCU TMS320F241PG heximal. This symmetrical nature and lack of ‘special optimal situations’ make programming with the PIC16C55X(A) simple yet efficient. In addition, the learning curve is reduced significantly.

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

Attack MCU AT91SAM7S256 Binary

Attack MCU AT91SAM7S256 Binary

Attack MCU AT91SAM7S256 and break microcontroller at91sam7s256 fuse bit, extract embeded Binary from ATMEL microprocessor flash and eeprom memory;

· Incorporates the ARM7TDMI® ARM® Thumb® Processor

– High-performance 32-bit RISC Architecture

– High-density 16-bit Instruction Set

– Leader in MIPS/Watt

– Embedded*ICE™ In-circuit Emulation, Debug Communication Channel Support

Internal High-speed Flash

– 256 kbytes, organized in 1024 Pages of 256 Bytes (AT91SAM7S256)

– 128 kbytes, organized in 512 Pages of 256 Bytes (AT91SAM7S128)

– 64 kbytes, organized in 512 Pages of 128 Bytes (AT91SAM7S64)

– 32 kbytes, organized in 256 Pages of 128 Bytes (AT91SAM7S321/32)

– Single Cycle Access at Up to 30 MHz in Worst Case Conditions

– Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed after break avr atmega64a MCU

– Page Programming Time: 6 ms, Including Page Auto-erase, Full Erase Time: 15 ms

– 10,000 Write Cycles, 10-year Data Retention Capability, Sector Lock Capabilities,

Flash Security Bit

– Fast Flash Programming Interface for High Volume Production

Internal High-speed SRAM, Single-cycle Access at Maximum Speed

– 64 kbytes (AT91SAM7S256)

– 32 kbytes (AT91SAM7S128)

– 16 kbytes (AT91SAM7S64)

– 8 kbytes (AT91SAM7S321/32)

Memory Controller (MC)

– Embedded Flash Controller, Abort Status and Misalignment Detection

Reset Controller (RSTC)

– Based on Power-on Reset and Low-power Factory-calibrated Brown-out Detector

– Provides External Reset Signal Shaping and Reset Source Status

Clock Generator (CKGR)

– Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL

Power Management Controller (PMC)

– Software Power Optimization Capabilities, Including Slow Clock Mode (Down to 500 Hz) and Idle Mode

– Three Programmable External Clock Signals

Advanced Interrupt Controller (AIC)

– Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

– Two (AT91SAM7S256/128/64/321) or One (AT91SAM7S32) External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected Debug Unit (DBGU)

– 2-wire UART and Support for Debug Communication Channel interrupt,

Programmable ICE Access Prevention by break microcontroller atmega128 hex

Periodic Interval Timer (PIT)

– 20-bit Programmable Counter plus 12-bit Interval Counter Windowed Watchdog (WDT)

– 12-bit key-protected Programmable Counter

– Provides Reset or Interrupt Signals to the System

– Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

Eleven (AT91SAM7S256/128/64/321) or Nine (AT91SAM7S32) Peripheral DMA Controller (PDC) Channels

One USB 2.0 Full Speed (12 Mbits per Second) Device Port (Except for the AT91SAM7S32).

– On-chip Transceiver, 328-byte Configurable Integrated FIFOs

One Synchronous Serial Controller (SSC)

– Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

– I²S Analog Interface Support, Time Division Multiplex Support

– High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

Two (AT91SAM7S256/128/64/321) or One (AT91SAM7S32) Universal Synchronous/Asynchronous Receiver Transmitters (USART)

– Individual Baud Rate Generator, IrDA® Infrared Modulation/Demodulation

– Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

– Manchester Encoder/Decoder (AT91SAM7S256/128)

– Full Modem Line Support on USART1 (AT91SAM7S256/128/64/321)

One Master/Slave Serial Peripheral Interface (SPI)

– 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

One Three (AT91SAM7S256/128/64/321)-channel or Two (AT91SAM7S32)-channel 16-bit Timer/Counter (TC)

– Three (AT91SAM7S256/128/64/321) or One (AT91SAM7S32) External Clock Inputs, Two Multi-purpose I/O Pins per Channel before Attack MCU

– Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

One Four-channel 16-bit PWM Controller (PWMC)

One Two-wire Interface (TWI)

– Master Mode Support Only, All Two-wire Atmel EEPROMs Supported

One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os

SAM-BA™ Boot Assistant

– Default Boot program

– Interface with SAM-BA Graphic User Interface

IEEE 1149.1 JTAG Boundary Scan on All Digital Pins if Attack MCU

5V-tolerant I/Os, including Four High-current Drive I/O lines, Up to 16 mA Each

Power Supplies

– Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components

– 3.3V or 1.8V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply

– 1.8V VDDCORE Core Power Supply with Brown-out Detector

Fully Static Operation: Up to 55 MHz at 1.65V and 85° C Worst Case Conditions

Available in a 64-lead LQFP Green Package (AT91SAM7S256/128/64/321) and 48-lead LQFP Green Package (AT91SAM7S32).