Archive for the ‘Recover MCU’ Category

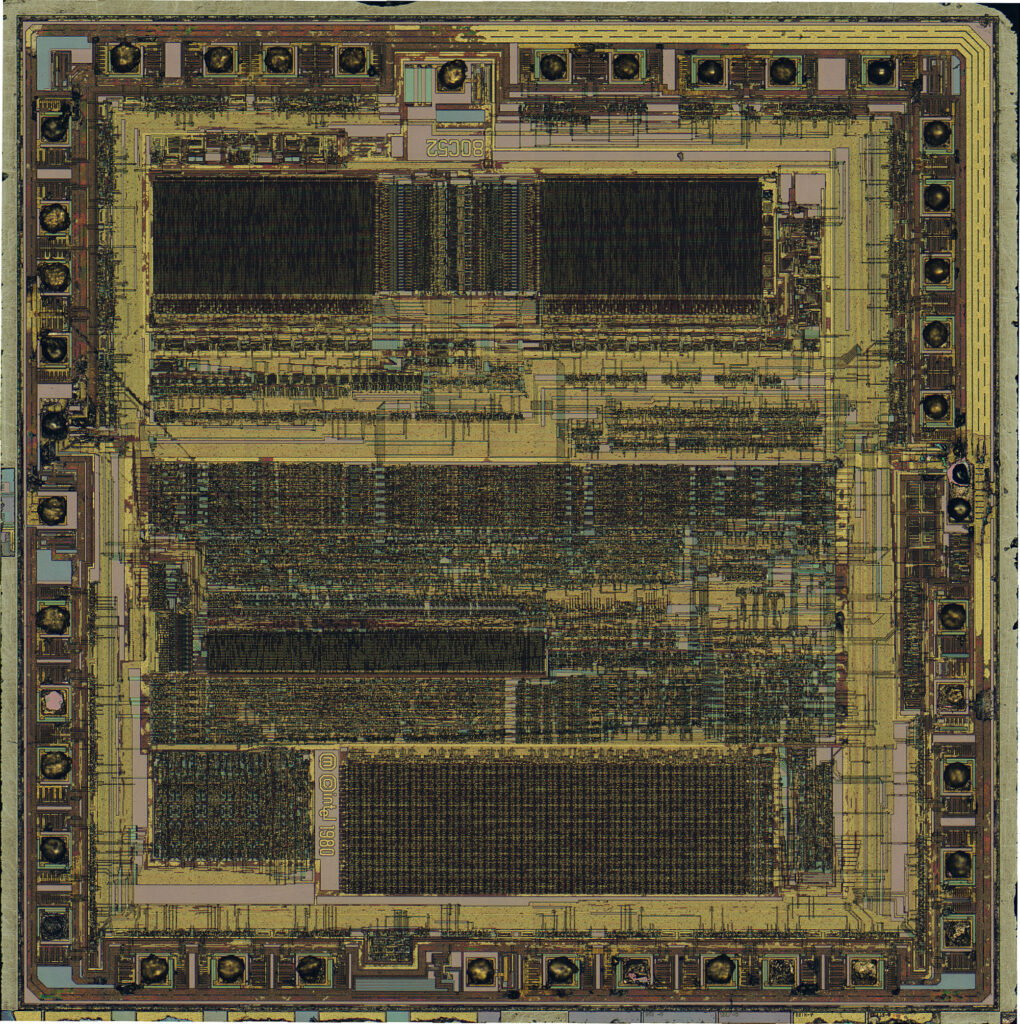

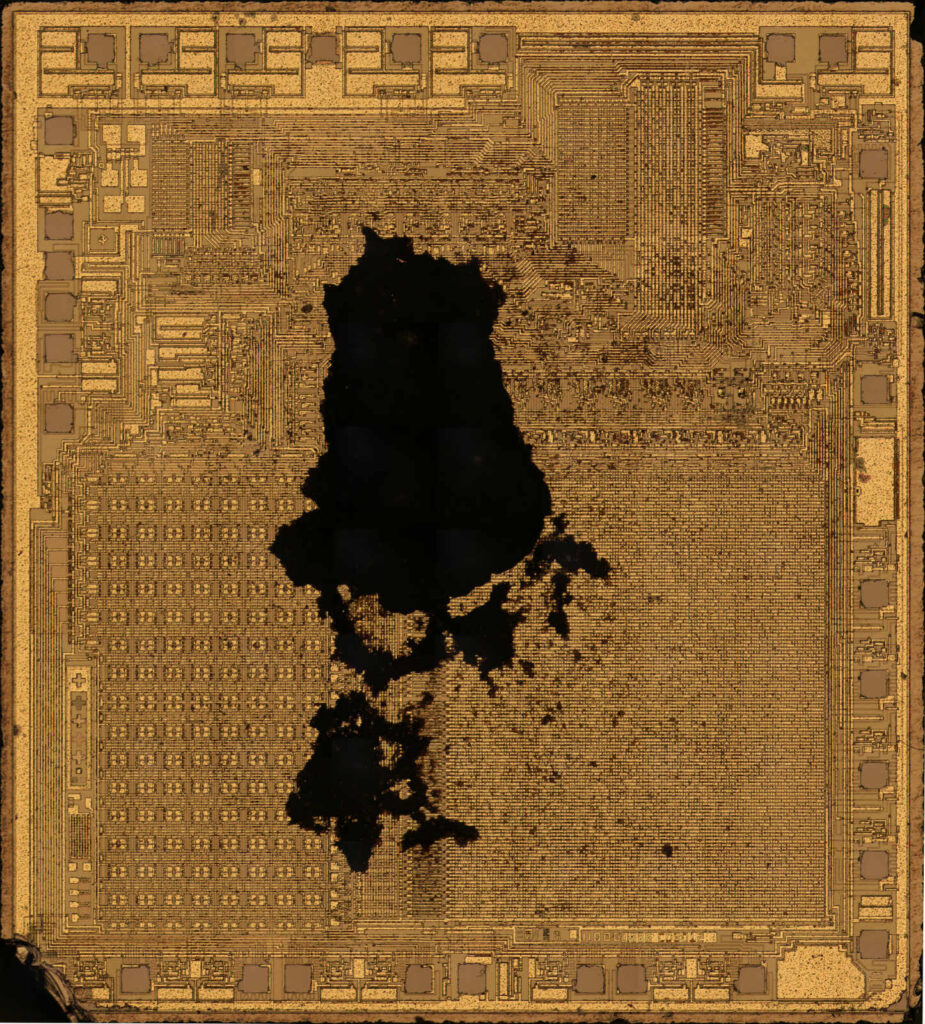

Reverse Engineering Chip PIC12C508 Code

Reverse Engineering Chip PIC12C508 Code

Reverse Engineering Chip PIC12C508 Code need to extract the embedded firmware from locked microcontroller pic12c508, then crack mcu protective system;

The recommendations of the maximum receiver baud rate error was made under the assumption that the Receiver and Transmitter equally divides the maximum total error. There are two possible sources for the receivers baud rate error. The Receiver’s system clock (XTAL) will always have some minor instability over the supply voltage range and the temperature range.

When using a crystal to generate the system clock, this is rarely a problem, but for a resonator the system clock may differ more than 2% depending of the resonators tolerance. The second source for the error is more controllable. The baud rate generator can not always do an exact division of the system frequency to get the baud rate wanted after copy mcu pic16f870 program.

In this case an UBRR value that gives an acceptable low error can be used if possible. Setting the Multi-processor Communication mode (MPCMn) bit in UCSRnA enables a filtering function of incoming frames received by the USART Receiver.

Frames that do not contain address information will be ignored and not put into the receive buffer. This effectively reduces the number of incoming frames that has to be handled by the CPU, in a system with multiple CHIPs that communicate via the same serial bus if attacking mcu c8051f530 firmware.

The Transmitter is unaffected by the MPCMn setting, but has to be used differently when it is a part of a system utilizing the Multi-processor Communication mode. If the Receiver is set up to receive frames that contain 5 to 8 data bits, then the first stop bit indicates if the frame contains data or address information. If the Receiver is set up for frames with nine data bits, then the ninth bit (RXB8n) is used for identifying address and data frames.

When the frame type bit (the first stop or the ninth bit) is one, the frame contains an address. When the frame type bit is zero the frame is a data frame.

The Multi-processor Communication mode enables several slave CHIPs to receive data from a master CHIP. This is done by first decoding an address frame to find out which CHIP has been addressed if attack microcontroller pic16c63a hex.

If a particular slave CHIP has been addressed, it will receive the following data frames as normal, while the other slave CHIPs will ignore the received frames until another address frame is received.

Reverse Microcontroller PIC12C508A Firmware

Reverse Microcontroller PIC12C508A Firmware

Reverse Microcontroller PIC12C508A structure and extract code from embedded mcu pic12c508a flash memory, decrypt the Firmware of pic12c508a microprocessor;

The clock recovery logic synchronizes internal clock to the incoming serial frames. Figure 87 illustrates the sampling process of the start bit of an incoming frame.

The sample rate is 16 times the baud rate for Normal mode, and eight times the baud rate for Double Speed mode. The horizontal arrows illustrate the synchronization variation due to the sampling process. Note the larger time variation when using the Double Speed mode (U2Xn = 1) of operation. Samples denoted zero are samples done when the RxDn line is idle (i.e., no communication activity).

Please shown in the figure. The clock recovery logic then uses samples 8, 9, and 10 for Normal mode, and samples 4, 5, and 6 for Double Speed mode (indicated with sample numbers inside boxes on the figure), to decide if a valid start bit is received.

If two or more of these three samples have logical high levels (the majority wins), the start bit is rejected as a noise spike and the Receiver starts looking for the next high to low-transition.

If however, a valid start bit is detected, the clock recovery logic is synchronized and the data recovery can begin. The synchronization process is repeated for each start bit before Breaking IC.

When the receiver clock is synchronized to the start bit, the data recovery can begin. The data recovery unit uses a state machine that has 16 states for each bit in Normal mode and eight states for each bit in Double Speed mode.

Figure 88 shows the sampling of the data bits and the parity bit. Each of the samples is given a number that is equal to the state of the recovery unit.The decision of the logic level of the received bit is taken by doing a majority voting of the logic value to the three samples in the center of the received bit when Restore IC program.

The center samples are emphasized on the figure by having the sample number inside boxes. The majority voting process is done as follows: If two or all three samples have high levels, the received bit is registered to be a logic 1.

If two or all three samples have low levels, the received bit is registered to be a logic 0. This majority voting process acts as a low pass filter for the incoming signal on the RxDn pin.

The recovery process is then repeated until a complete frame is received. Including the first stop bit. Note that the Receiver only uses the first stop bit of a frame.

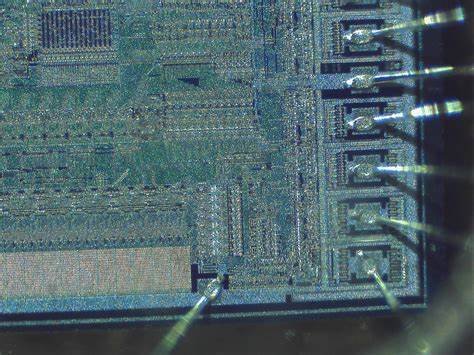

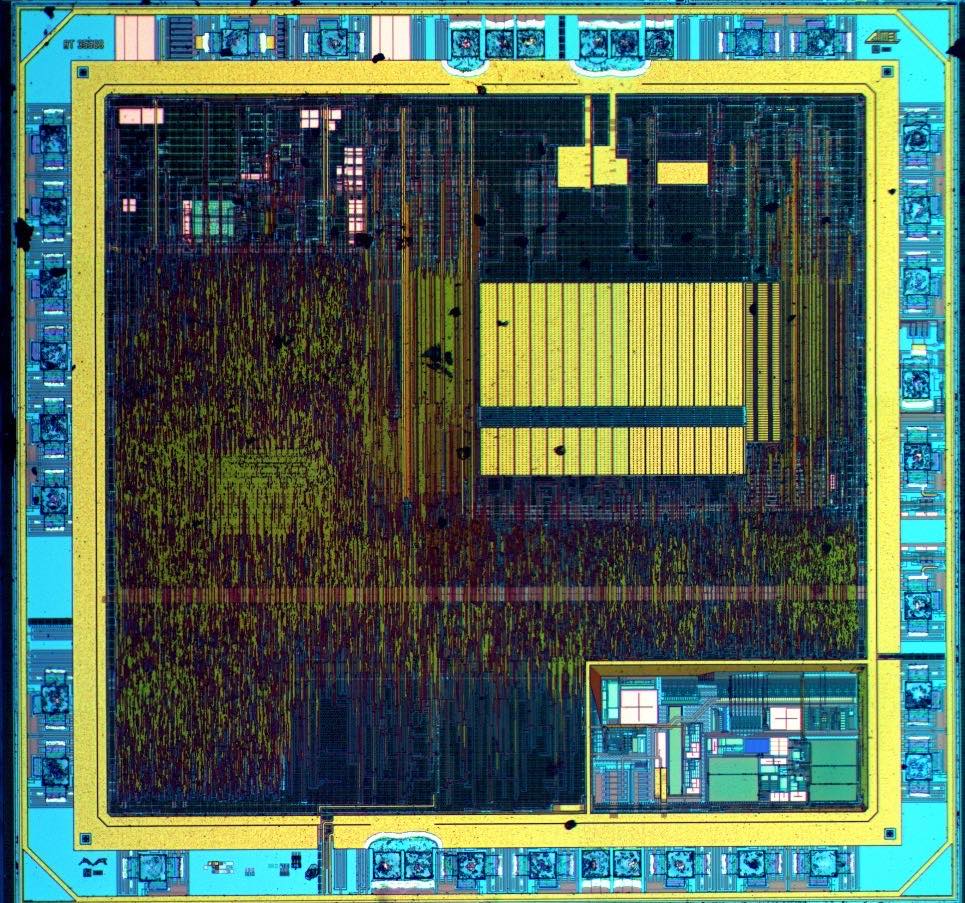

Reverse IC ATmega162P Eeprom

Reverse IC ATmega162P Eeprom

Reverse IC ATmega162P Eeprom after crack microcontroller atmega162p protective system, and extract locked code from mcu atmega162p flash memory;

Internal clock generation is used for the asynchronous and the synchronous master modes of operation. The description in this section refers to Figure 84. The USART Baud Rate Register (UBRRn) and the down-counter connected to it function as a programmable prescaler or baud rate generator.

The down-counter, running at system clock (fosc), is loaded with the UBRRn value each time the counter has counted down to zero or when the UBRRLn Register is written. A clock is generated each time the counter reaches zero. This clock is the baud rate generator clock output (= fosc/(UBRRn+1)). The Transmitter divides the baud rate generator clock output by 2, 8 or 16 depending on mode. The baud rate generator output is used directly by the Receiver’s clock and data recovery units after Reverse IC eeprom.

However, the recovery units use a state machine that uses 2, 8 or 16 states depending on mode set by the state of the UMSELn, U2Xn and DDR_XCKn bits. Table 98 contains equations for calculating the baud rate (in bits per second) and for calculating the UBRRn value for each mode of operation using an internally generated clock source after reverse Ic eeprom.

The transfer rate can be doubled by setting the U2Xn bit in UCSRnA. Setting this bit only has effect for the asynchronous operation. Set this bit to zero when using synchronous operation if reverse ic eeprom.

Setting this bit will reduce the divisor of the baud rate divider from 16 to 8, effectively doubling the transfer rate for asynchronous communication. Note however that the Receiver will in this case only use half the number of samples (reduced from 16 to 8) for data sampling and clock recovery, and therefore a more accurate baud rate setting and system clock are required when this mode is used. For the Transmitter, there are no downsides after Reverse IC eeprom.

External clocking is used by the synchronous slave modes of operation. The description in this section refers to Figure 84 for details. External clock input from the XCKn pin is sampled by a synchronization register to minimize the chance of meta-stability. The output from the synchronization register must then pass through an edge detector before it can be used by the Transmitter and Receiver when Reverse IC eeprom.

This process introduces a two CPU clock period delay and therefore the maximum external XCKn clock frequency is limited by the following equation when Reverse IC eeprom:

Note that fosc depends on the stability of the system clock source. It is therefore recommended to add some margin to avoid possible loss of data due to frequency variations.

When synchronous mode is used (UMSELn = 1), the XCKn pin will be used as either clock input (Slave) or clock output (Master). The dependency between the clock edges and data sampling or data change is the same. The basic principle is that data input (on RxDn) is sampled at the opposite XCKn clock edge of the edge the data output (TxDn) is changed when Reverse IC eeprom.

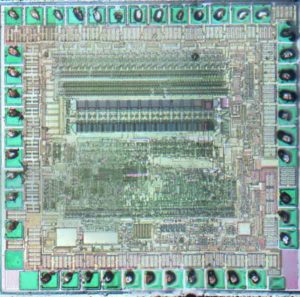

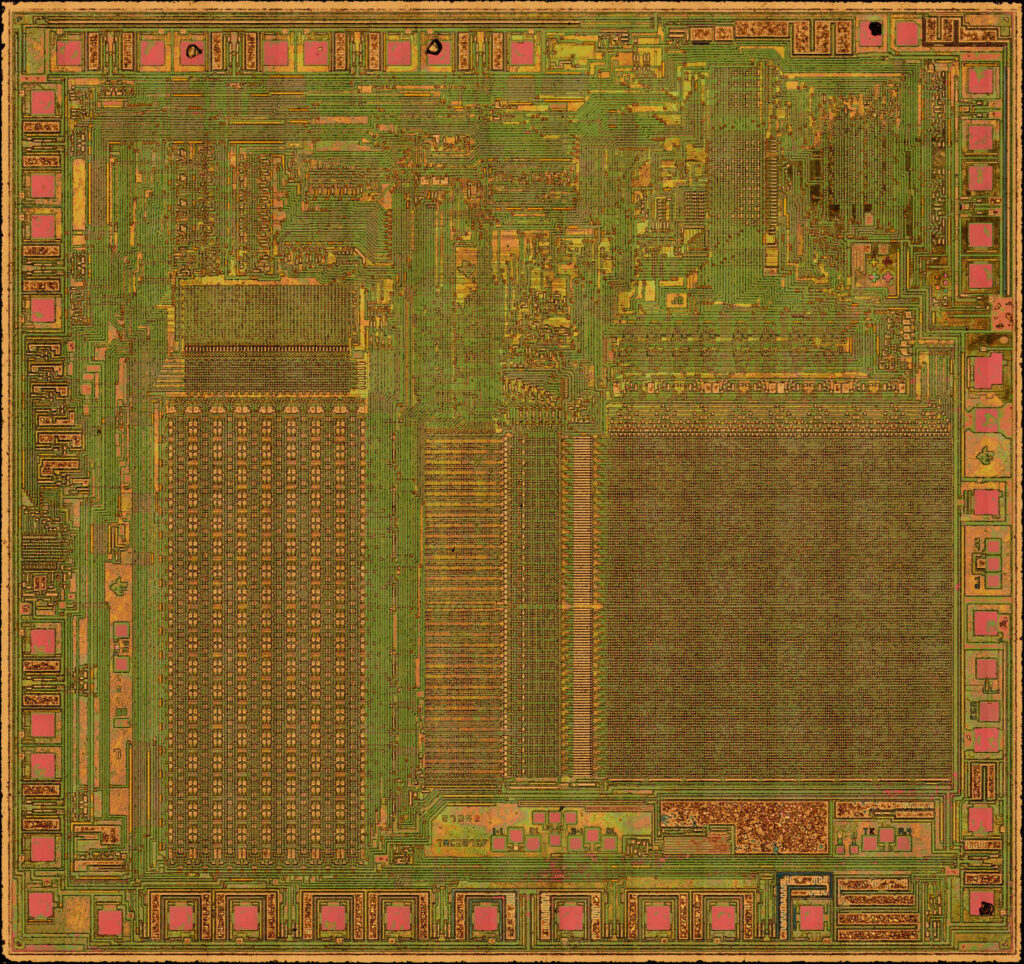

Recover MCU PIC16F628 Firmware

Recover MCU PIC16F628 Firmware

Recover MCU PIC16F628 Firmware needs to unlock microcontroller pic16f628 protective memory and then readout embedded firmware from mcu pic16f628 flash memory;

We can Recover MCU PIC16F628 Firmware, please view the MCU PIC16F628 features for your reference:

The PIC16F62X are 18-Pin FLASH-based members of the versatile PIC16CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers. All PICmicro® microcontrollers employ an advanced RISC architecture.

The PIC16F62X have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data.

The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16F62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class. PIC16F62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

There are eight oscillator configurations, of which the single pin ER oscillator provides a low-cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, INTRC is a self-contained internal oscillator and the HS is for High Speed crystals.

The SLEEP (power-down) mode offers power savings. The user can wake up the chip from SLEEP through several external and internal interrupts and reset.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

Table 1-1 shows the features of the PIC16F62X mid-range microcontroller families. A simplified block diagram of the PIC16F62X is shown in Figure 3-1.

The PIC16F62X series fits in applications ranging from battery chargers to low-power remote sensors. The FLASH technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient.

The small footprint packages make this microcontroller series ideal for all applications with space limitations. Low-cost, low-power, high-performance, ease of use and I/O flexibility make the PIC16F62X very versatile.

The PIC16F62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A Third Party “C” compiler support tool is also available.

Reverse Microcontroller ATmega8P Archive

Reverse Microcontroller ATmega8P Archive

Reverse Microcontroller ATmega8P Archive needs to crack mcu atmega8p protective system and then extract locked code from mcu atmega8p flash memory;

The dashed boxes in the block diagram separate the three main parts of the USART (listed from the top): Clock Generator, Transmitter and Receiver.

Control Registers are shared by all units. The Clock Generation logic consists of synchronization logic for external clock input used by synchronous slave operation, and the baud rate generator if Recover atmega164pa MCU code.

The XCKn (Transfer Clock) pin is only used by synchronous transfer mode. The Transmitter consists of a single write buffer, a serial Shift Register, Parity Generator and Control logic for handling different serial frame formats.

The write buffer allows a continuous transfer of data without any delay between frames. The Receiver is the most complex part of the USART module due to its clock and data recovery units.

The recovery units are used for asynchronous data reception. In addition to the recovery units, the Receiver includes a Parity Checker, Control logic, a Shift Register and a two level receive buffer (UDRn).

The Receiver supports the same frame formats as the Transmitter, and can detect Frame Error, Data OverRun and Parity Errors if break microcontroller atmega324a binary.

The Clock Generation logic generates the base clock for the Transmitter and Receiver. The USARTn supports four modes of clock operation: Normal asynchronous, Double Speed asynchronous, Master synchronous and Slave synchronous mode.

The UMSELn bit in USART Control and Status Register C (UCSRnC) selects between asynchronous and synchronous operation. Double Speed (asynchronous mode only) is controlled by the U2Xn found in the UCSRnA Register.

When using synchronous mode (UMSELn = 1), the Data Direction Register for the XCKn pin (DDR_XCKn) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCKn pin is only active when using synchronous mode.

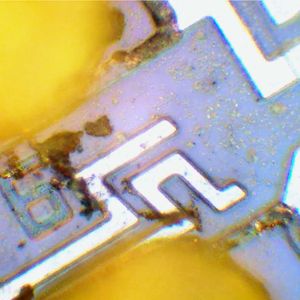

Reverse MCU ATmega461PV Binary

Reverse MCU ATmega461PV Binary

Reverse MCU ATmega461PV and readout microcontroller atmega461pv secured Binary, crack mcu protective system and using focus ion beam to cut off the security fuse bit;

The interconnection between Master and Slave CPUs with SPI is shown in Figure 80. The system consists of two shift Registers, and a Master clock generator. Th e SPI Master initiates the communication cycle when pulling low the Slave Select SS pin of the desired Slave.

Master and Slave prepare the data to be sent in their respective shift Registers, and the Master generates the required clock pulses on the SCK line to interchange data if break atmega64pa MCU binary.

Data is always shifted from Master to Slave on the Master Out – Slave In, MOSI, line, and from Slave to Master on the Master In – Slave Out, MISO, line. After each data packet, the Master will synchronize the Slave by pulling high the Slave Select, SS, line.

When configured as a Master, the SPI interface has no automatic control of the SS line. This must be handled by user software before communication can start. When this is done, writing a byte to the SPI Data Register starts the SPI clock generator, and the hardware shifts the eight bits into the Slave. After shifting one byte, the SPI clock generator stops, setting the end of Transmission Flag (SPIF) after break atmega128a MCU firmware.

If the SPI Interrupt Enable bit (SPIE) in the SPCR Register is set, an interrupt is requested. The Master may continue to shift the next byte by writing it into SPDR, or signal the end of packet by pulling high the Slave Select, SS line. The last incoming byte will be kept in the Buffer Register for later use. When configured as a Slave, the SPI interface will remain sleeping with MISO tri-stated as long as the SS pin is driven high. In this state, software may update the contents of the SPI Data Register, SPDR, bu t the data will not be shifted out by incoming clock pulses on the SCK pin until the SS pin is driven low.

As one byte has been completely shifted, the end of Transmission Flag, SPIF is set. If the SPI Interrupt Enable bit, SPIE, in the SPCR Register is set, an interrupt is requested.

The Slave may continue to place new data to be sent into SPDR before reverseing the incoming data. The last incoming byte will be kept in the Buffer Register for later use. The system is single buffered in the transmit direction and double buffered in the receive direction. This means that bytes to be transmitted cannot be written to the SPI Data Register before the entire shift cycle is completed.

When receiving data, however, a received character must be reverse from the SPI Data Register before the next character has been completely shifted in. Otherwise, the first byte is lost.

In SPI Slave mode, the control logic will sample the incoming signal of the SCK pin. To ensure correct sampling of the clock signal, the frequency of the SPI clock should never exceed fosc/4.

Reverse Chip ATmega461V Program

Reverse Chip ATmega461V Program

Reverse Chip ATmega461V and read mcu atmega461v flash Program, the fuse bit of atmega461v microcontroller will be broken to reset the status of MCU from locked to unlocked one;

The clock source for Timer/Counter2 is named clkT2S. clkT2S is by default connected to the main system I/O clock clkIO. By setting the AS2 bit in ASSR, Timer/Counter2 is asynchronously clocked from the TOSC1 pin.

This enables use of Timer/Counter2 as a Real Time Counter (RTC). When AS2 is set, pins TOSC1 and TOSC2 are disconnected from Port C if Reverse chip atmega861v code.

A crystal can then be connected between the TOSC1 and TOSC2 pins to serve as an independent clock source for Timer/Counter2. The Oscillator is optimized for use with a 32.768 kHz crystal. Applying an external clock source to TOSC1 is not recommended.

For Timer/Counter2, the possible prescaled selections are: clkT2S/8, clkT2S/32, clkT2S/64, clkT2S/128, clkT2S/256, and clkT2S/1024. Additionally, clkT2S as well as 0 (stop) may be selected after Reverse mcu atmega261 hex.

Setting the PSRASY bit in GTCCR resets the prescaler. This allows the user to operate with a predictable prescaler. When this bit is one, the Timer/Counter2 prescaler will be reset.

This bit is normally cleared immediately by hardware. If the bit is written when Timer/Counter2 is operating in asynchronous mode, the bit will remain one until the prescaler has been reset.

The bit will not be cleared by hardware if the TSM bit is set. Refer to the description of the “Bit 7– TSM: Timer/Counter Synchronization Mode” on page 170 for a description of the Timer/Counter Synchronization mode when Reverse CHIP PROGRAM.

The Serial Peripheral Interface (SPI) allows high-speed synchronous data transfer between the ATmega461v and peripheral devices or between several AVR devices. The ATmega640/1280/1281/2560/2561 SPI includes the following features:

Full-duplex, Three-wire Synchronous Data Transfer

Master or Slave Operation

LSB First or MSB First Data Transfer

Seven Programmable Bit Rates

End of Transmission Interrupt Flag

Write Collision Flag Protection

Wake-up from Idle Mode

Double Speed (CK/2) Master SPI Mode when Reverse CHIP PROGRAM

USART can also be used in Master SPI mode, see “USART in SPI Mode” on page 231. The Power Reduction SPI bit, PRSPI, in “Power Reduction Register 0 – PRR0” on page 54 on page 50 must be written to zero to enable SPI module.

Reverse MCU ATMEGA261 Heximal

Reverse MCU ATMEGA261 Heximal

We can Reverse Mcu ATMEGA261 Heximal, please view the Mcu ATMEGA261 features for your reference:

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024). The extreme values for the OCR2A Register represent special cases when generating a PWM waveform output in the fast PWM mode.

If the OCR2A is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2A equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM2A1:0 bits.) when Reverse Mcu Heximal.

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC2x to toggle its logical level on each compare match (COM2x1:0 = 1). The waveform generated will have a maximum frequency of foc2 = fclk_I/O/2 when OCR2A is set to zero if Reverse Mcu Heximal.

This feature is similar to the OC2A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode. The phase correct PWM mode (WGM22:0 = 1 or 5) provides a high resolution phase correct PWM waveform generation option before Reverse Mcu Heximal.

The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to TOP and then from TOP to BOTTOM. TOP is defined as 0xFF when WGM22:0 = 1, and OCR2A when MGM22:0 = 5. In non-inverting Compare Output mode, the Output Compare (OC2x) is cleared on the compare match between TCNT2 and OCR2x while upcounting, and set on the compare match while downcounting after Reverse Mcu Heximal.

In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications if Reverse Mcu Heximal.

In phase correct PWM mode the counter is incremented until the counter value matches TOP. When the counter reaches TOP, it changes the count direction. The TCNT2 value will be equal to TOP for one timer clock cycle. The timing diagram for the phase correct PWM mode is shown on Figure 73 before Reverse Mcu Heximal.

The TCNT2 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2 when Reverse Mcu Heximal.

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches BOTTOM. The Interrupt Flag can be used to generate an interrupt each time the counter reaches the BOTTOM value. In phase correct PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM. An inverted PWM output can be generated by setting the COM2x1:0 to three. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when MGM2:0 = 7 (See Table 87 on page 185). The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output if Reverse Mcu Heximal.

The PWM waveform is generated by clearing (or setting) the OC2x Register at the compare match between OCR2x and TCNT2 when the counter increments, and setting (or clearing) the OC2x Register at compare match between OCR2x and TCNT2 when the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation.

Reverse Engineering Chip ATmega2560L Software

Reverse Engineering Chip ATmega2560L Software

Reverse Engineering Chip ATmega2560L Software is actually a process to read encrypted heximal from mcu atmega2560L flash memory after crack microcontroller atmega2560L security fuse bit;

The Timer/Counter can be clocked by an internal synchronous or an external asynchronous clock source. The clock source clkT2 is by default equal to the MCU clock, clkI/O.

When the AS2 bit in the ASSR Register is written to logic one, the clock source is taken from the Timer/Counter Oscillator connected to TOSC1 and TOSC2. For details on asynchronous operation, see “Asynchronous Status Register – ASSR” on page 189 if attack attiny2313 mcu firmware.

For details on clock sources and prescaler, see “Timer/Counter Prescaler” on page 193. The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit.

Figure 68 shows a block diagram of the counter and its surrounding environment. Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock (clkT2). clkT2 can be generated from an external or internal clock source, selected by the Clock Select bits (CS22:0) before attack atmega64l mcu flash.

When no clock source is selected (CS22:0 = 0) the timer is stopped. However, the TCNT2 value can be accessed by the CPU, regardless of whether clkT2 is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM21 and WGM20 bits located in the Timer/Counter Control Register (TCCR2A) and the WGM22 located in the Timer/Counter Control Register B (TCCR2B).

There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC2A and OC2B. For more details about advanced counting sequences and waveform generation, see “Modes of Operation” on page 178.

The Timer/Counter Overflow Flag (TOV2) is set according to the mode of operation selected by the WGM22:0 bits. TOV2 can be used for generating a CPU interrupt.

The 8-bit comparator continuously compares TCNT2 with the Output Compare Register (OCR2A and OCR2B). Whenever TCNT2 equals OCR2A or OCR2B, the comparator signals a match. A match will set the Output Compare Flag (OCF2A or OCF2B) at the next timer clock cycle.

If the corresponding interrupt is enabled, the Output Compare Flag generates an Output Compare interrupt. The Output Compare Flag is automatically cleared when the interrupt is executed.

Alternatively, the Output Compare Flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the WGM22:0 bits and Compare Output mode (COM2x1:0) bits.

The max and bottom signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation (“Modes of Operation” on page 178). Figure 58 on page 154 shows a block diagram of the Output Compare unit.

Reverse Engineering MCU ATmega1281P Firmware

Reverse Engineering MCU ATmega1281P Firmware

Reverse Engineering MCU ATmega1281P and copy embedded Firmware from microcontroller atmega1281p memory to new MCU, to make microprocessor atmega1281p cloning units.

The Timer/Counter Overflow Flag (TOVn) is set at the same timer clock cycle as the OCRnx Registers are updated with the double buffer value (at BOTTOM).

When either OCRnA or ICRn is used for defining the TOP value, the OCnA or ICFn Flag set when TCNTn has reached TOP. The Interrupt Flags can then be used to generate an interrupt each time the counter reaches the TOP or BOTTOM value.

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the Compare Registers. If the TOP value is lower than any of the Compare Registers, a compare match will never occur between the TCNTn and the OCRnx before attack microcontroller mc68hc705p6a memory.

As Figure 57 shows the output generated is, in contrast to the phase correct mode, symmetrical in all periods. Since the OCRnx Registers are updated at BOTTOM, the length of the rising and the falling slopes will always be equal. This gives symmetrical output pulses and is therefore frequency correct.

Using the ICRn Register for defining TOP works well when using fixed TOP values. By using ICRn, the OCRnA Register is free to be used for generating a PWM output on OCnA before copying pic16lf877 MCU program.

However, if the base PWM frequency is actively changed by changing the TOP value, using the OCRnA as TOP is clearly a better choice due to its double buffer feature.

In phase and frequency correct PWM mode, the compare units allow generation of PWM waveforms on the OCnx pins. Setting the COMnx1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COMnx1:0 to three.

crack locked microcontroller ATMEGA1281 memory and clone its heximal file from program flash and data eeprom

The actual OCnx value will only be visible on the port pin if the data direction for the port pin is set as output (DDR_OCnx). The PWM waveform is generated by setting (or clearing) the OCnx Register at the compare match between OCRnx and TCNTn when the counter increments, and clearing (or setting) the OCnx Register at compare match between OCRnx and TCNTn when the counter decrements.

The PWM frequency for the output when using phase and frequency correct PWM can be calculated by the following equation:

The N variable represents the prescaler divider (1, 8, 64, 256, or 1024). The extreme values for the OCRnx Register represents special cases when generating a PWM waveform output in the phase correct PWM mode.

If the OCRnx is set equal to BOTTOM the output will be continuously low and if set equal to TOP the output will be set to high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values. If OCR1A is used to define the TOP value (WGM13:0 = 9) and COM1A1:0 = 1, the OC1A output will toggle with a 50% duty cycle.