Archive for the ‘Recover MCU’ Category

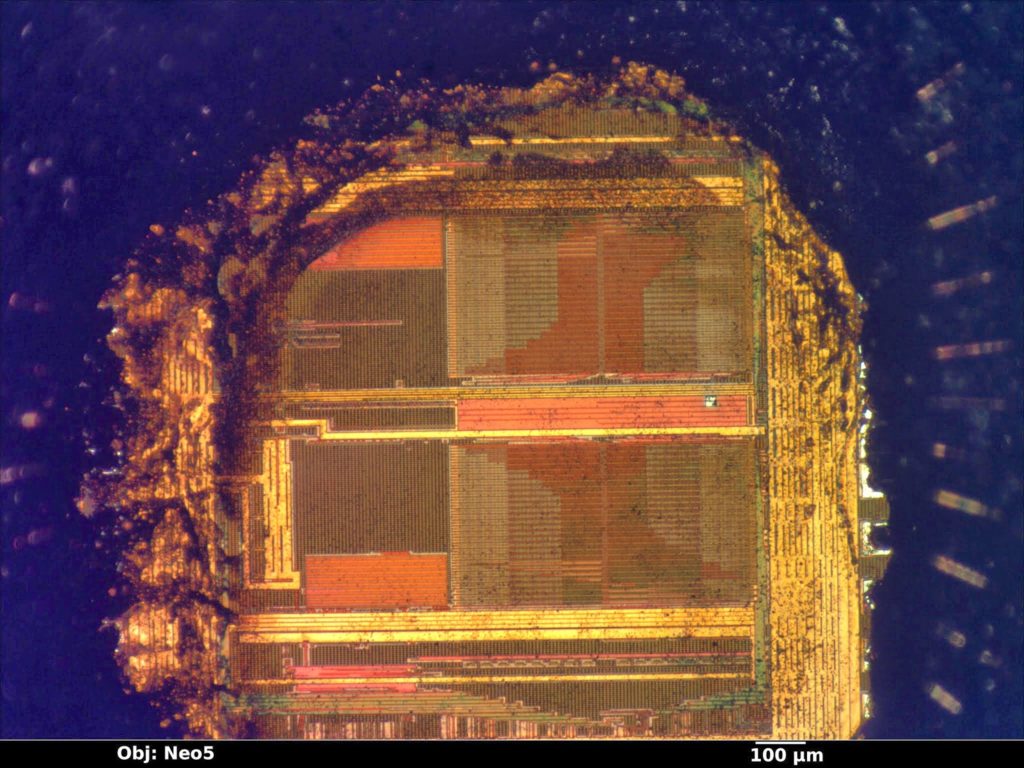

Reverse Engineering Chip ATmega644A Code

Reverse Engineering Chip ATmega644A Code

Reverse Engineering Chip ATmega644A and extract microcontroller scheme to locate the security fuse bit of embedded flash, cut it off by breaking MCU technique, read processor atmega644a code and make new microprocessor cloning;

When the SM2..0 bits are written to 000, the SLEEP instruction makes the Chip enter Idle mode, stopping the CPU but allowing the SPI, USART, Analog Comparator, ADC, 2-wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue operating. This sleep mode basically halts clkCPU and clkFLASH, while allowing the other clocks to run. Idle mode enables the Chip to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and USART Transmit Complete interrupts.

If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Status Register – ACSR. This will reduce power consumption in Idle mode. If the ADC is enabled, a conversion starts automatically when this mode is entered before attack mcu protection.

When the SM2..0 bits are written to 001, the SLEEP instruction makes the Chip enter ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the external interrupts, 2-wire Serial Interface address match, Timer/Counter2 and the Watchdog to continue operating (if enabled). This sleep mode basically halts clkI/O, clkCPU, and clk-FLASH, while allowing the other clocks to run.

This improves the noise environment for the ADC, enabling higher resolution measurements. If the ADC is enabled, a conversion starts automatically when this mode is entered when Reverse Engineering Chip code.

Apart form the ADC Conversion Complete interrupt, only an External Reset, a Watchdog System Reset, a Watchdog interrupt, a Brown-out Reset, a 2-wire serial interface interrupt, a Timer/Counter2 interrupt, an SPM/EEPROM ready interrupt, an external level interrupt on INT7:4 or a pin change interrupt can wakeup the Chip from ADC Noise Reduction mode.

When the SM2..0 bits are written to 010, the SLEEP instruction makes the Chip enter Power-down mode. In this mode, the external Oscillator is stopped, while the external interrupts, the 2-wire Serial Interface, and the Watchdog continue operating (if enabled).

Only an External Reset, a Watchdog Reset, a Brown-out Reset, 2-wire Serial Interface address match, an external level interrupt on INT7:4, an external interrupt on INT3:0, or a pin change interrupt can wake up the Chip. This sleep mode basically halts all generated clocks, allowing operation of asynchronous modules only after Reverse Engineering MICROCONTROLLER.

Reverse Engineering Microcontroller AVR ATXMEGA128A1 Heximal

Reverse Engineering Microcontroller AVR ATXMEGA128A1 Heximal

We can reverse engineering Microcontroller AVR ATXMEGA128A1 Heximal, please view the Microcontroller AVR ATXMEGA128A1 features for your reference:

The External Bus Interface (EBI) is the interface for connecting external peripheral and memory to the data memory space. The XMEGA A1 has 3 ports that can be used for the EBI. It can interface external SRAM, SDRAM, and/or peripherals such as LCD displays and other memory mapped devices if the heximal of microcontroller can be reverse engineeringed.

The address space, and the number of pins used, for the external memory is selectable from 256 bytes (8-bit) and up to 16M bytes (24-bit). Various multiplexing modes for address and data lines can be selected for optimal use of pins when more or less pins is available for the EBI when REVERSE ENGINEERING MICROCONTROLLER.

Each of the four chip selects has seperate configuration, and can be configured for SRAM, SRAM Low Pin Count (LPC) or SDRAM. The data memory address space associated for each chip select is decided by a configurable base address and address size for each chip celect.

For SDRAM both 4-bit SDRAM is supported, and SDRAM configurations such as CAS Latency and Refresh rate is configurable in software. The EBI is clocked from the Peripheral 2x Clock, running up to two times faster than the CPU and supporting speeds of up to 64 MHz.

The Calibration Row is a seperate memory section for factory programmed data. It contains calibration data for functions such as oscillators, device ID, and a factory programmed serial number that is unique for each device. The device ID for the available XMEGA A1 devices is shown in Table 7-1 on page 13. Some of the calibration values will be automatically loaded to the corresponding module or peripheral unit during reset. The Calibration Row can not be written or erased. It can be read from application software and external programming from reverse engineering the heximal out of microcontroller.

Restore Atmel Controller ATmega88P Source Code

Restore Atmel Controller ATmega88P Source Code

We can restore Atmel controller ATMEGA88P source code, please view the Atmel controller ATMEGA88P features for your reference:

The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. After four clock cycles the source code vector address for the actual interrupt handling routine is executed. During this four clock cycle period, the source code Counter is pushed onto the Stack.

The vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by four clock cycles if Restore Atmel Controller ATmega88P Source Code.

This increase comes in addition to the start-up time from the selected sleep mode. A return from an interrupt handling routine takes four clock cycles. During these four clock cycles, the source code Counter (two bytes) is popped back from the Stack, the Stack Pointer is incremented by two, and the I-bit in SREG is set.

The ATmega48/88/168 contains 4/8/16K bytes On-Atmel controller In-System Resource codemable Flash memory for source code storage. Since all AVR instructions are 16 or 32 bits wide, the Flash is organized as 2/4/8K x 16. For software security, the Flash source code memory space is divided into two sections, Boot Loader Section and Application source code Section in ATmega88.

ATmega48 does not have separate Boot Loader and Application source code sections, and the SPM instruction can be executed from the entire Flash. The Flash memory has an endurance of at least 10,000 write/erase cycles. The ATmega48/88/168 source code Counter (PC) is 11/12/13 bits wide, thus addressing the 2/4/8K source code memory locations. The operation of Boot source code section and associated Boot Lock bits when Restore Atmel Controller ATmega88P Source Code.

The ATmega48/88/168 is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in the Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 – 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

The lower 768/1280/1280 data memory locations address both the Register File, the I/O memory, Extended I/O memory, and the internal data SRAM. The first 32 locations address the Register File, the next 64 location the standard I/O memory, then 160 locations of Extended I/O memory, and the next 512/1024/1024 locations address the internal data SRAM before Restore Atmel Controller ATmega88P Source Code.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space. The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register. When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X, Y, and Z are decremented or incremented. The 32 general purpose working registers, 64 I/O Registers, 160 Extended I/O Registers, and the 512/1024/1024 bytes of internal data SRAM in the ATmega48/88/168 when RECOVER MCU.

Decrypt Embedded Microcontroller Eeprom Memory

Decrypt Embedded Microcontroller Eeprom Memory

decrypt embedded microcontroller eeprom memory, as we mentioned above, embedded microcontroller decrypter can use laser scanning to read the status of transistors. And just embedded microcontroller decrypter expected, laser can scan the P and N type transistor’s source in the embedded microcontroller memorizer as well as the photocurrent generated from the drain electrode, un-transparent metal wire can be use to treat the lowest photocurrent.

The result of laser scanning can see the photocurrent in the inverse switch status of SRAM unit obviously whembedded microcontrollerh can be used to assure the embedded microcontroller memorizer status after decrypting it. In order to explain the result for the purpose of pursuit more proper scanning parameters, use DIODE-2D present the laser impulse to two dimension of reversor after Decrypt Embedded Microcontroller Eeprom Memory.

The length of narrow channel is assumed to be 1 micron, laser radiation strength is 1.104W/cm2. Other parameters, such as mixed density, P and N channel depth, use the standard 1 micron N type base CMOS technology parameter of embedded microcontroller.

Embedded microcontroller decrypter has simulate the two status of reversor, the laser with different wavelength on the various locations, their relationship with the power supply current can reveal that the current of transistor in the turn off exposure status could be much bigger than the current in the turn on exposure status when Decrypt Embedded Microcontroller Eeprom Memory. Turn up the shutdown transistor channel can increase the total current and its increasing amount is much bigger than the slightly decrease the open channel resistor slight.

Reverse Engineering Microchip Processor TS80C54X2 Flash Code

Reverse Engineering Microchip Processor TS80C54X2 Flash Code

We can reverse engineering microchip processor TS80C54X2 flash code, please view the microchip processor TS80C54X2 features for your reference:

The Timer0 module has the following features:

8-bit timer/counter register, TMR0 Readable and writable

8-bit software programmable prescaler Internal or external clock select:

– Edge select for external clock

– External clock from either the T0CKI pin or from the output of the comparator

Figure 7-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler) after Reverse Engineering Microchip Processor TS80C54X2 Flash Code.

If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3).

The user can work around this by writing an adjusted value to the TMR0 register.

There are two types of Counter mode. The first Counter mode uses the T0CKI pin to increment Timer0. It is selected by setting the T0CS bit (OPTION<5>), setting the CMPT0CS bit (CMCON0<4>) and setting the COUTEN bit (CMCON0<6>).

In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge.

Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.1 “Using Timer0 with an External Clock (TS80C54X2)”.

The second Counter mode uses the output of the comparator to increment Timer0. It can be entered in two different ways. The first way is selected by setting the T0CS bit (OPTION<5>) and clearing the CMPT0CS bit (CMCON<4>) before Reverse Engineering Microchip Processor TS80C54X2 Flash Code;

(COUTEN [CMCON<6>]) does not affect this mode of operation. This enables an internal connection between the comparator and the Timer0.

The second way is selected by setting the T0CS bit (OPTION<5>), setting the CMPT0CS bit (CMCON0<4>) and clearing the COUTEN bit (CMCON0<6>).

This allows the output of the comparator onto the T0CKI pin, while keeping the T0CKI input active. Therefore, any comparator change on the COUT pin is fed back into the T0CKI input. The T0SE bit (OPTION<4>) determines the source edge before Reverse Engineering Microchip Processor TS80C54X2 Flash Code.

Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input as discussed in Section 7.1 “Using Timer0 with an External Clock (TS80C54X2)”

Read Atmel IC ATmega16A Locked Code

Read Atmel IC ATmega16A Locked Code

We can read atmel IC ATMEGA16A locked code, please view the atmel IC ATMEGA16A features for your reference:

The atmel IC ATMEGA16A devices incorporate an on-chip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD, or program the pin as GP3.

An internal weak pull-up resistor is implemented using a transistor (refer to Table 12-2 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified.

See Section 12.0 “Electrical Characteristics” for details. When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature,…) must be met to ensure operation after Read Atmel IC ATmega16A Locked Code.

If these conditions are not met, the devices must be held in Reset until the operating parameters are met. A simplified block diagram of the on-chip Power-on Reset circuit. The Power-on Reset circuit and the Device Reset Timer (see Section 9.5 “Device Reset Timer (DRT)”) circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high.

After the time-out period, which is typically 18 ms, it will reset the Reset latch and thus end the on-chip Reset signal. A power-up example where MCLR is held low is shown in Figure 9-3. VDD is allowed to rise and stabilize before bringing MCLR high.

The chip will actually come out of Reset TDRT msec after MCLR goes high. In Figure 9-4, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3) when Read Atmel IC ATmega16A Locked Code.

The VDD is stable before the Start-up Timer times out and there is no problem in getting a proper Reset. However, Figure 9-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the Start-up Timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times if RECOVER MCU.

Replicate Atmel AVR Controller ATmega168P Eeprom Code

Replicate Atmel AVR Controller ATmega168P Eeprom Code

We can replicate Atmel AVR controller ATMEGA168P eeprom code, please view the Atmel AVR controller ATMEGA168P features for your reference:

This Configuration bit, when unprogrammed (left in the ‘1’ state), enables the external MCLR function. When programmed, the MCLR function is tied to the internal VDD and the pin is assigned to be a I/O..

The ATMEGA168P devices incorporate an on-chip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD, or program the pin as GP3.

An internal weak pull-up resistor is implemented using a transistor (refer to Table 12-2 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create a Power-on Reset before replicate Atmel AVR controller ATMEGA168P eeprom code.

A maximum rise time for VDD is specified. See Section 12.0 “Electrical Characteristics” for details. When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature,…) must be met to ensure operation.

If these conditions are not met, the devices must be held in Reset until the operating parameters are met. A simplified block diagram of the on-chip Power-on Reset circuit. The Power-on Reset circuit and the Device Reset Timer (see Section 9.5 “Device Reset Timer (DRT)”) circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high if replicate Atmel AVR controller ATMEGA168P eeprom code.

After the time-out period, which is typically 18 ms, it will reset the Reset latch and thus end the on-chip Reset signal. A power-up example where MCLR is held low is shown in Figure 9-3. VDD is allowed to rise and stabilize before bringing MCLR high.

The chip will actually come out of Reset TDRT msec after MCLR goes high. In Figure 9-4, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3).

The VDD is stable before the Start-up Timer times out and there is no problem in getting a proper Reset. However, Figure 9-5 depicts a problem situation where VDD rises too slowly.

The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the Start-up Timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly when replicate Atmel AVR controller ATMEGA168P eeprom code.

For such situations, we recommend that external RC circuits be used to achieve longer POR delay times.

Restore AVR Controller ATtiny24 Encrypted Heximal

Restore AVR Controller ATtiny24 Encrypted Heximal

We can restore avr controller ATTINY24 encrypted heximal, please view the avr controller ATTINY24 features for your reference:

If the code protection bit has not been encrypted HEX, the on-chip encrypted heximal memory can be read out for verification purposes.

The first 64 locations and the last location (Reset vector) can be read, regardless of the code protection bit setting.

Four memory locations are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Restore AVR Controller ATtiny24 Encrypted Heximal.

Use only the lower 4 bits of the ID locations and always encrypted heximal the upper 8 bits as ‘0’s. The ATTINY24 microcontrollers can be serially encrypted heximalmed while in the end application circuit.

This is simply done with two lines for clock and data, and three other lines for power, ground and the encrypted heximalming voltage. This allows customers to manufacture boards with unencrypted heximalmed devices and then encrypted heximal the microcontroller just before shipping the product.

This also allows the most recent firmware or a custom firmware, to be encrypted heximalmed. The devices are placed into a encrypted heximal/Verify mode by holding the GP1 and GP0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see encrypted heximalming specification) if Restore AVR Controller ATtiny24 Encrypted Heximal.

GP1 becomes the encrypted heximalming clock and GP0 becomes the encrypted heximalming data. Both GP1 and GP0 are Schmitt Trigger inputs in this mode. After Reset, a 6-bit command is then supplied to the device.

Depending on the command, 16 bits of encrypted heximal data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial encrypted heximalming, please refer to the ATTINY24 encrypted heximalming Specifications after RECOVER MCU.

Recover ATMEL AVR ATTINY44V Flash Code

Recover ATMEL AVR ATTINY44V Flash Code

We can recover ATMEL AVR ATTINY44V flash code, please view the ATMEL AVR ATTINY44V features for your reference:

The MPASM Assembler is a full-featured, universal macro assembler for all ATTINY44Vs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

· Integration into MPLAB IDE projects

· User-defined macros to streamline assembly code

· Conditional assembly for multi-purpose source files if Recover ATMEL AVR ATTINY44V Flash Code

· Directives that allow complete control over the assembly process

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for ATTINY44V family of ATMEL AVRs and the ATTINY44V family of digital signal controllers.

These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers. For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for ATTINY44V devices. MPLAB C30 C Compiler uses the assembler to produce its object file when Recover ATMEL AVR ATTINY44V Flash Code.

The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

· Support for the entire ATTINY44V instruction set

· Support for fixed-point and floating-point data

· Command line interface

· Rich directive set

· Flexible macro language

· MPLAB IDE compatibility before RECOVER MCU

Recover AVR Chip ATTINY4313 Embedded Data

Recover AVR Chip ATTINY4313 Embedded Data

We can recover AVR Chip ATTINY4313 embedded data, please view the AVR Chip ATTINY4313 features for your reference:

The ATtiny4313 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny4313 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU) before recover AVR Chip, allowing two independent registers to be accessed in one single instruction executed in one clock cycle.

The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers after Recover AVR Chip ATTINY4313 Embedded Data.

The ATtiny4313 provides the following features: 2/4K bytes of In-System Programmable Flash, 128/256 bytes EEPROM, 128/256 bytes SRAM, 18 general purpose I/O lines, 32 general purpose working registers.

A single-wire Interface for On-chip Debugging, two flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, Universal Serial Interface with Start Condition Detector, a programmable Watchdog Timer with internal Oscillator, and three software selectable power saving modes when Recover AVR Chip ATTINY4313 Embedded Data.

The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or hardware reset.

In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption after Recover MCU.