Archive for the ‘Recover Chip’ Category

Reverse Engineering MCU Chip ATmega1284P Flash

Reverse Engineering MCU Chip ATmega1284P Flash

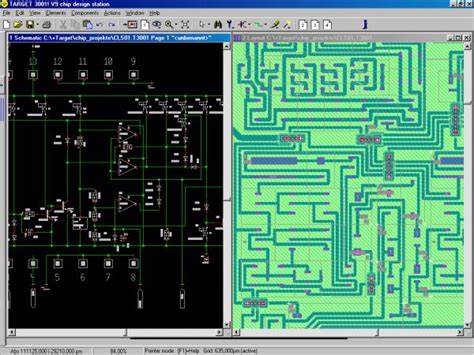

Reverse Engineering MCU Chip ATmega1284P which is executed in the reverse order of microcontroller manufacturing, read Flash code from microcontroller ATmega1284P memory, and make ATmega1284P MCU cloning;

Most port pins have alternate functions in addition to being general digital I/Os. Figure 37 shows how the port pin control signals from the simplified Figure 34 can be overridden by alternate functions.

The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR mcu chip family.

When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01) if attack mcu attiny2313 firmware.

See “Configuring the Pin” on page 82 for more details about this feature. OC0A, Output Compare Match A output: The PB7 pin can serve as an external output for the Timer/Counter0 Output Compare.

The pin has to be configured as an output (DDB7 set “one”) to serve this function. The OC0A pin is also the output pin for the PWM mode timer function.

OC1C, Output Compare Match C output: The PB7 pin can serve as an external output for the Timer/Counter1 Output Compare C.

The pin has to be configured as an output (DDB7 set (one)) to serve this function. The OC1C pin is also the output pin for the PWM mode timer function.

PCINT7, Pin Change Interrupt source 7: The PB7 pin can serve as an external interrupt source. OC1B, Output Compare Match B output: The PB6 pin can serve as an external output for the Timer/Counter1 Output Compare B. The pin has to be configured as an output (DDB6 set (one)) to serve this function.

The OC1B pin is also the output pin for the PWM mode timer function when Reverse engineering Mcu chip. PCINT6, Pin Change Interrupt source 6: The PB7 pin can serve as an external interrupt source.

Recover Microcontroller ATmega644P Flash

Recover Microcontroller ATmega644P Flash

Recover Microcontroller ATmega644P Flash memory content is a process to extract ATmega644p MCU memory heximal by crack processor’s fuse bit;

To further ensure program security, alterations to the Watchdog set-up must follow timed sequences. The sequence for clearing WDE and changing time-out configuration is as follows:

(WDCE) and WDE. A logic one must be written to WDE regardless of the previous value of the WDE bit. (WDP) as desired, but with the WDCE bit cleared. This must be done in one operation.

The following code example shows one assembly and one C function for turning off the Watchdog Timer. The example assumes that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during the execution of these functions if break Microcontroller pic16f628a content.

Note: If the Watchdog is accidentally enabled, for example by a runaway pointer or brown-out condition, the device will be reset and the Watchdog Timer will stay enabled. If the code is not set up to handle the Watchdog, this might lead to an eternal loop of time-out resets.

To avoid this situation, the application software should always clear the Watchdog System Reset Flag (WDRF) and the WDE control bit in the initialisation routine, even if the Watchdog is not in use. In the same operation, write a logic one to the Watchdog change enable bit to attack pic12f510 program.

Recover MCU ATmega644PA Flash

Recover MCU ATmega644PA Flash

Recover MCU ATmega644PA Flash memory content after crack microcontroller ATmega644PA protection and extract code from microprocessor ATmega644PA memory.

When the BOD is enabled, and VCC decreases to a value below the trigger level (VBOT- in Figure 29), the Brown-out Reset is immediately activated. When VCC increases above the trigger level (VBOT+ in Figure 29), the delay counter starts the MCU after the Time- out period tTOUT has expired if recover mcu pic18f452 program.

The BOD circuit will only detect a drop in VCC if the voltage stays below the trigger level for longer than tBOD given in Table 23. When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration.

On the falling edge of this pulse, the delay timer starts counting the Time-out period tTOUT. See “Watchdog Timer” on page 56. for details on operation of the Watchdog Timer after break chip pic12cr509a flash.

ATmega644PA features an internal bandgap reference. This reference is used for Brown-out Detection, and it can be used as an input to the Analog Comparator or the ADC.

The voltage reference has a start-up time that may influence the way it should be used. The start-up time is given in Table 26. To save power, the reference is not always turned The reference is on during the following situations if attack dsp mcu tms320f241pg heximal:

When the BOD is enabled (by programming the BODLEVEL [2..0] Fuse).

When the bandgap reference is connected to the Analog Comparator (by setting the ACBG bit in ACSR) before recover mcu flash. When the ADC is enabled.

Thus, when the BOD is not enabled, after setting the ACBG bit or enabling the ADC, the user must always allow the reference to start up before the output from the Analog Comparator or ADC is used.

To reduce power consumption in Power-down mode, the user can avoid the three conditions above to ensure that the reference is turned off before entering Power-down mode when recover mcu flash. ATmega644PA has an Enhanced Watchdog Timer (WDT). The main features are:

Clocked from separate On-chip Oscillator

3 Operating modes

– Interrupt

– System Reset

– Interrupt and System Reset

Extract Chip ATmega324PA Code

Extract Chip ATmega324PA Code

Extract Chip ATmega324PA Code from embedded program memory after unlock chip atmega324pa.

Bit 7 – PRTWI: Power Reduction TWI

Writing a logic one to this bit shuts down the TWI by stopping the clock to the module. When waking up the TWI again, the TWI should be re initialized to ensure proper operation.

Bit 6 – PRTIM2: Power Reduction Timer/Counter2

Writing a logic one to this bit shuts down the Timer/Counter2 module in synchronous mode (AS2 is 0). When the Timer/Counter2 is enabled, operation will continue like before the shutdown if recover mcu atmega164pa code.

Bit 5 – PRTIM0: Power Reduction Timer/Counter0

Writing a logic one to this bit shuts down the Timer/Counter0 module. When the Timer/Counter0 is enabled, operation will continue like before the shutdown.

Bit 4 – Res: Reserved bit

This bit is reserved bit and will always read as zero.

Bit 3 – PRTIM1: Power Reduction Timer/Counter1

Writing a logic one to this bit shuts down the Timer/Counter1 module. When the Timer/Counter1 is enabled, operation will continue like before the shutdown after reverse engineering chip atmega324 code.

Bit 2 – PRSPI: Power Reduction Serial Peripheral Interface

Writing a logic one to this bit shuts down the Serial Peripheral Interface by stopping the clock to the module. When waking up the SPI again, the SPI should be re initialized to ensure proper operation.

Bit 1 – PRUSART0: Power Reduction USART0

Writing a logic one to this bit shuts down the USART0 by stopping the clock to the module. When waking up the USART0 again, the USART0 should be re initialized to ensure proper operation.

Bit 0 – PRADC: Power Reduction ADC

Writing a logic one to this bit shuts down the ADC. The ADC must be disabled before shut down. The analog comparator cannot use the ADC input MUX when the ADC is shut down.

Bit 7..6 – Res: Reserved bits

These bits are reserved and will always read as zero.

Bit 5 – PRTIM5: Power Reduction Timer/Counter5

Writing a logic one to this bit shuts down the Timer/Counter5 module. When the Timer/Counter5 is enabled, operation will continue like before the shutdown if break microcontroller atmega324a bin.

Bit 4 – PRTIM4: Power Reduction Timer/Counter4

Writing a logic one to this bit shuts down the Timer/Counter4 module. When the Timer/Counter4 is enabled, operation will continue like before the shutdown.

Bit 3 – PRTIM3: Power Reduction Timer/Counter3

Writing a logic one to this bit shuts down the Timer/Counter3 module. When the Timer/Counter3 is enabled, operation will continue like before the shutdown.

Bit 2 – PRUSART3: Power Reduction USART3

Writing a logic one to this bit shuts down the USART3 by stopping the clock to the module. When waking up the USART3 again, the USART3 should be re initialized to ensure proper operation.

Bit 1 – PRUSART2: Power Reduction USART2

Writing a logic one to this bit shuts down the USART2 by stopping the clock to the module. When waking up the USART2 again, the USART2 should be re initialized to ensure proper operation.

Bit 0 – PRUSART1: Power Reduction USART1

Writing a logic one to this bit shuts down the USART1 by stopping the clock to the module. When waking up the USART1 again, the USART1 should be re initialized to ensure proper operation.

Recovery MCU ATmega324V Code

Recovery MCU ATmega324V Code

Recovery MCU ATmega324V Code from flash memory, the microcontroller ATmega324V code extraction will be carried out after MCU ATmega324V cracking;

The device can utilize a 32.768 kHz watch crystal as clock source by a dedicated Low Frequency Crystal Oscillator. The crystal should be connected as shown in Figure 22.

When this Oscillator is selected, start-up times are determined by the SUT Fuses and CKSEL0 as shown in Table 13 before break PIC16F716 MCU Heximal.

The calibrated internal RC Oscillator by default provides a 8.0 MHz clock. The frequency is nominal value at 3V and 25°C. The device is shipped with the CKDIV8 Fuse programmed.

See “System Clock Prescaler” on page 48 for more details. This clock may be selected as the system clock by programming the CKSEL Fuses as shown in Table when copy pic16f886 Mcu firmware

If selected, it will operate with no external components. During reset, hardware loads the calibration byte into the OSCCAL Register and thereby automatically calibrates the RC Oscillator. At 3V and 25°C, this calibration gives a frequency of 8 MHz ± 1%.

The oscillator can be calibrated to any frequency in the range 7.3 – 8.1 MHz within ±1% accuracy, by changing the OSCCAL register.

When this Oscillator is used as the mcu clock, the Watchdog Oscillator will still be used for the Watchdog Timer and for the Reset Time-out. For more information on the pre-programmed calibration value, see the section “Calibration Byte” on page 338 before attack atmega162 Mcu flash.

The device is shipped with this option selected.

The frequency ranges are preliminary values. Actual values are TBD.

If 8 MHz frequency exceeds the specification of the device (depends on VCC); The CKDIV8 Fuse can be programmed in order to divide the internal frequency by 8. When this Oscillator is selected, start-up times are determined by the SUT Fuses.

The Oscillator Calibration Register is used to trim the Calibrated Internal RC Oscillator to remove process variations from the oscillator frequency. The factory-calibrated value is automatically written to this register during mcu reset, giving an oscillator frequency of 8.0 MHz at 25°C. The application software can write this register to change the oscillator frequency.

The oscillator can be calibrated to any frequency in the range 7.3 – 8.1 MHz within ±1% accuracy. Calibration outside that range is not guaranteed.

Note that this oscillator is used to time EEPROM and Flash write accesses, and these write times will be affected accordingly. If the EEPROM or Flash are written, do not calibrate to more than 8.8 MHz. Otherwise, the EEPROM or Flash write may fail.

The CAL7 bit determines the range of operation for the oscillator. Setting this bit to 0 gives the lowest frequency range, setting this bit to 1 gives the highest frequency range.

The two frequency ranges are overlapping, in other words a setting of OSCCAL = 0x7F gives a higher frequency than OSCCAL = 0x80.

The CAL6..0 bits are used to tune the frequency within the selected range. A setting of 0x00 gives the lowest frequency in that range, and a setting of 0x7F gives the highest frequency in the range. Incrementing CAL6..0 by 1 will give a frequency increment of less than 2% in the frequency range 7.3 – 8.1 MHz.

Reverse Engineering IC ATmega164V Code

Reverse Engineering IC ATmega164V Code

Reverse Engineering IC ATmega164V Code and extract MCU ATmega164V heximal from embedded program memory and data memory, clone ATmega164V code to new microcontroller.

The device is shipped with internal RC oscillator at 8.0MHz and with the fuse CKDIV8 programmed, resulting in 1.0MHz system clock. The startup time is set to maximum and time-out period enabled.

(CKSEL = “0010”, SUT = “10”, CKDIV8 = “0”). The default setting ensures that all users can make their desired clock source setting using any available programming interface if Recover IC STM32F107RCT6 code.

Any clock source needs a sufficient VCC to start oscillating and a minimum number of oscillating cycles before it can be considered stable.

To ensure sufficient VCC, the device issues an internal reset with a time-out delay (tTOUT) after the device reset is released by all other reset sources. “On-chip Debug System” on page 56 describes the start conditions for the internal reset if copy microcontroller PIC16F684 firmware.

The delay (tTOUT) is timed from the Watchdog Oscillator and the number of cycles in the delay is set by the SUTx and CKSELx fuse bits. The selectable delays are shown in Table 8. The frequency of the Watchdog Oscillator is voltage dependent as shown in “ATmega164 Typical Characteristics – Preliminary Data”.

Main purpose of the delay is to keep the AVR in reset until it is supplied with minimum Vcc. The delay will not monitor the actual voltage and it will be required to select a delay longer than the Vcc rise time. If this is not possible, an internal or external Brown-Out Detection circuit should be used after Recover chip pic16f913 binary.

A BOD circuit will ensure sufficient Vcc before it releases the reset, and the time-out delay can be disabled. Disabling the time-out delay without utilizing a Brown-Out Detection circuit is not recommended.

The oscillator is required to oscillate for a minimum number of cycles before the clock is considered stable. An internal ripple counter monitors the oscillator output clock, and keeps the internal reset active for a given number of clock cycles. The reset is then released and the device will start to execute.

The recommended oscillator start-up time is dependent on the clock type, and varies from 6 cycles for an externally applied clock to 32K cycles for a low frequency crystal.

The start-up sequence for the clock includes both the time-out delay and the start-up time when the device starts up from reset. When starting up from Power-save or Power down mode, Vcc is assumed to be at a sufficient level and only the start-up time is included.

Pins XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an On-chip Oscillator, as shown in Figure 22. Either a quartz crystal or a ceramic resonator may be used.

This Crystal Oscillator is a low power oscillator, with reduced voltage swing on the XTAL2 output. It gives the lowest power consumption, but is not capable of driving other clock inputs, and may be more susceptible to noise in noisy environments. In these cases, refer to the “Full Swing Crystal Oscillator” on page 43.

C1 and C2 should always be equal for both crystals and resonators. The optimal value of the capacitors depends on the crystal or resonator in use, the amount of stray capacitance, and the electromagnetic noise of the environment. Some initial guidelines for choosing capacitors for use with crystals are given in Table 9. For ceramic resonators, the capacitor values given by the manufacturer should be used.

Recover MCU ATmega164PA Code

Recover MCU ATmega164PA Code

Recover MCU ATmega164PA Code from secured flash memory of Microcontroller ATmega164PA and then clone the firmware of ATmega164PA processor;

Since the external memory is mapped after the internal memory as shown in Figure 14, the external memory is not addressed when addressing the first 8,704 bytes of data space.

It may appear that the first 8,704 bytes of the external memory are inaccessible (external memory addresses 0x0000 to 0x21FF). However, when connecting an external memory smaller than 64 KB, for example 32 KB, these locations are easily accessed simply by addressing from address 0x8000 to 0xA1FF.

Since the External Memory Address bit A15 is not connected to the external memory, addresses 0x8000 to 0xA1FF will appear as addresses 0x0000 to 0x21FF for the external memory before attacking MCU protection mechanism.

Addressing above address 0xA1FF is not recommended, since this will address an external memory location that is already accessed by another (lower) address. To the Application software, the external 32 KB memory will appear as one linear 32 KB address space from 0x2200 to 0xA1FF. This is illustrated in Figure 20.

Since the External Memory is mapped after the Internal Memory as shown in Figure 14,only 56KB of External Memory is available by default (address space 0x0000 to 0x21FF is reserved for internal memory). However, it is possible to take advantage of the entire External Memory by masking the higher address bits to zero.

This can be done by using the XMMn bits and control by software the most significant bits of the address. By setting Port C to output 0x00, and releasing the most significant bits for normal Port Pin operation, the Memory Interface will address 0x0000 – 0x2FFF. See the following code examples if Restore MCU program.

Care must be exercised using this option as most of the memory is masked away. Figure 21 presents the principal clock systems in the AVR and their distribution. All of the clocks need not be active at a given time. In order to reduce power consumption, the clocks to modules not being used can be halted by using different sleep modes, as described in “Power Management and Sleep Modes” on page 51. The clock systems are detailed below.

The CPU clock is routed to parts of the system concerned with operation of the AVR core. Examples of such modules are the General Purpose Register File, the Status Register and the data memory holding the Stack Pointer. Halting the CPU clock inhibits the core from performing general operations and calculations.

The I/O clock is used by the majority of the I/O modules, like Timer/Counters, SPI, and USART. The I/O clock is also used by the External Interrupt module, but note that some external interrupts are detected by asynchronous logic, allowing such interrupts to be detected even if the I/O clock is halted.

Also note that start condition detection in the USI module is carried out asynchronously when clkI/O is halted, TWI address recognition in all sleep modes.

The Flash clock controls operation of the Flash interface. The Flash clock is usually active simultaneously with the CPU clock. The Asynchronous Timer clock allows the Asynchronous Timer/Counter to be clocked directly from an external clock or an external 32 kHz clock crystal.

The dedicated clock domain allows using this Timer/Counter as a real-time counter even when the device is in sleep mode. The ADC is provided with a dedicated clock domain. This allows halting the CPU and I/O clocks in order to reduce noise generated by digital circuitry.

This gives more accurate ADC conversion results. The device has the following clock source options, selectable by Flash Fuse bits as shown below. The clock from the selected source is input to the AVR clock generator, and routed to the appropriate modules.

Break Chip ATmega164A Code

Break Chip ATmega164A Code

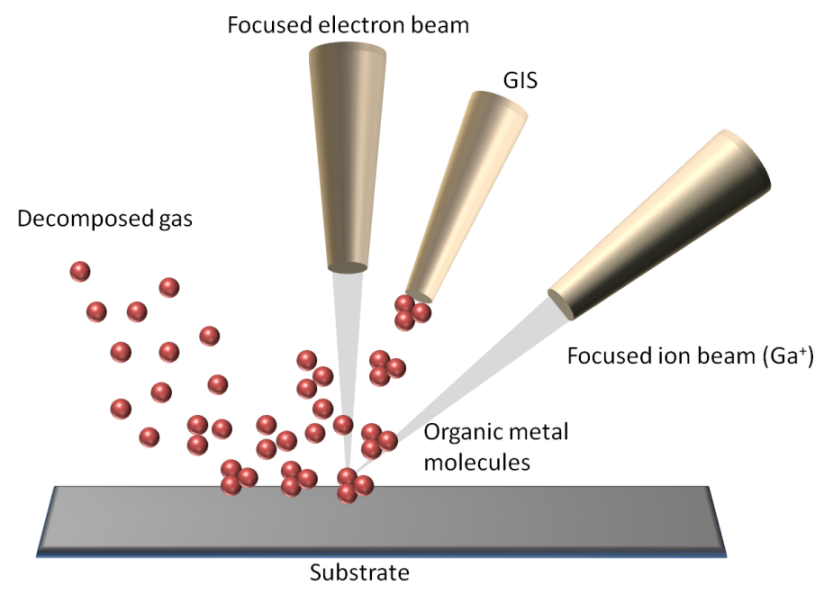

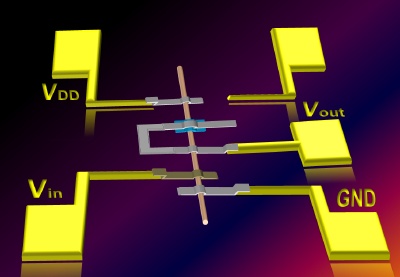

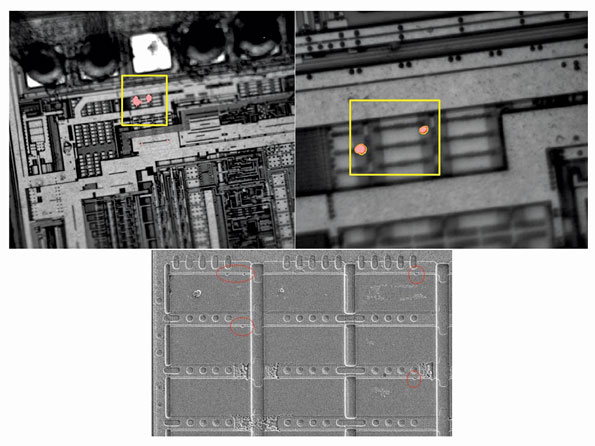

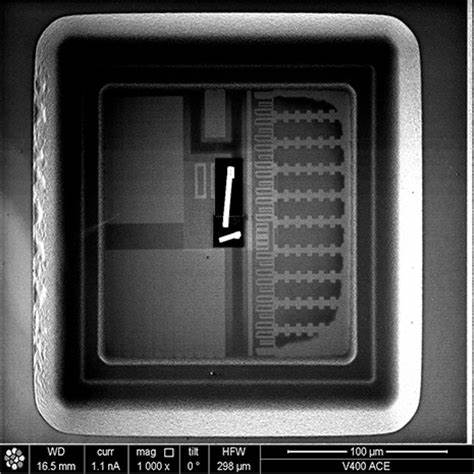

Break Chip ATmega164A protective system and extract microcontroller ATmega164A Code from flash memory, the ATmega164A MCU unlocking process will be carried out by focus ion beam;

External Memory devices have different timing requirements. To meet these requirements, the XMEM interface provides four different wait-states as shown in Table 5. It is important to consider the timing specification of the External Memory device before selecting the wait-state.

The most important parameters are the access time for the external memory compared to the set-up requirement. The access time for the External Memory is defined to be the time from receiving the chip select/address until the data of this address actually is driven on the bus if Break microcontroller s3f9454 software.

The access time cannot exceed the time from the ALE pulse must be asserted low until data is stable during a read sequence (See tLLRL+ tRLRH – tDVRH in Tables 169 through Tables 176 on pages 376 – 378).

The different wait-states are set up in software. As an additional feature, it is possible to divide the external memory space in two sectors with individual wait-state settings.

This makes it possible to connect two different memory devices with different timing requirements to the same XMEM interface. For XMEM interface timing details, please refer to Table 169 to Table 176 and Figure 161 to Figure 164 in the “External Data Memory Timing” on page 376 after read mcu pic16f688 software.

Note that the XMEM interface is asynchronous and that the waveforms in the following figures are related to the internal system clock. The skew between the internal and external clock (XTAL1) is not guarantied (varies between devices temperature, and supply voltage). Consequently, the XMEM interface is not suited for synchronous operation.

Bit 7 – SRE: External SRAM/XMEM Enable

Writing SRE to one enables the External Memory Interface.The pin functions AD7:0, A15:8, ALE, WR, and RD are activated as the alternate pin functions. The SRE bit overrides any pin direction settings in the respective data direction registers. Writing SRE to zero, disables the External Memory Interface and the normal pin and data direction set-tings are used.

Bit 6..4 – SRL2:0: Wait-state Sector Limit

It is possible to configure different wait-states for different External Memory addresses. The external memory address space can be divided in two sectors that have separate wait-state bits. The SRL2, SRL1, and SRL0 bits select the split of the sectors, see Table 4 and Figure 14.

By default, the SRL2, SRL1, and SRL0 bits are set to zero and the entire external memory address space is treated as one sector. When the entire SRAM address space is configured as one sector, the wait-states are configured by the SRW11 and SRW10 bits.

Bit 7– XMBK: External Memory Bus-keeper Enable

Writing XMBK to one enables the bus keeper on the AD7:0 lines. When the bus keeper is enabled, AD7:0 will keep the last driven value on the lines even if the XMEM interface has tri-stated the lines. Writing XMBK to zero disables the bus keeper. XMBK is not qualified with SRE, so even if the XMEM interface is disabled, the bus keepers are still activated as long as XMBK is one.

Bit 6..3 – Res: Reserved Bits

These bits are reserved and will always read as zero. When writing to this address location, write these bits to zero for compatibility with future devices.

Bit 2..0 – XMM2, XMM1, XMM0: External Memory High Mask

When the External Memory is enabled, all Port C pins are default used for the high address byte. If the full 60KB address space is not required to access the External Memory, some, or all, Port C pins can be released for normal Port Pin function as described in Table 6. As described in “Using all 64KB Locations of External Memory” on page 36, it is possible to use the XMMn bits to access all 64KB locations of the External Memory.

Recover Chip ATmega261A Program

Recover Chip ATmega261A Program

Recover Chip ATmega261A means the program of MCU ATmega261A from flash memory and eeprom memory will be readout and fuse bit of Microcontroller ATmega261A will be unlocked;

There are basically two types of interrupts. The first type is triggered by an event that sets the Interrupt Flag. For these interrupts, the Program Counter is vectored to the actual Interrupt Vector in order to execute the interrupt handling routine, and hardware clears the corresponding Interrupt Flag.

Interrupt Flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared. If an interrupt condition occurs while the corresponding interrupt enable bit is cleared, the Interrupt Flag will be set and remembered until the interrupt is enabled, or the flag is cleared by software if break mcu atmega64pa binary.

Similarly, if one or more interrupt conditions occur while the Global Interrupt Enable bit is cleared, the corresponding Interrupt Flag(s) will be set and remembered until the Global Interrupt Enable bit is set, and will then be executed by order of priority.

The second type of interrupts will trigger as long as the interrupt condition is present. These interrupts do not necessarily have Interrupt Flags. If the interrupt condition disappears before the interrupt is enabled, the interrupt will not be triggered after break ic atmega128a firmware.

When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served. Note that the Status Register is not automatChipally stored when entering an interrupt routine, nor restored when returning from an interrupt routine.

This must be handled by software. When using the CLI instruction to disable interrupts, the interrupts will be immediately disabled. No interrupt will be executed after the CLI instruction, even if it occurs simultaneously with the CLI instruction. The following example shows how this can be used to avoid interrupts during the timed EEPROM write sequence.

The interrupt execution response for all the enabled AVR interrupts is five clock cycles minimum. After five clock cycles the program vector address for the actual interrupt handling routine is executed. During these five clock cycle period, the Program Counter is pushed onto the Stack when Recover ic atmega168pa program.

The vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by five clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes five clock cycles. During these five clock cycles, the Program Counter (three bytes) is popped back from the Stack, the Stack Pointer is incremented by three, and the I-bit in SREG is set.

Recover MCU ATtiny88A Program

Recover MCU ATtiny88A Program

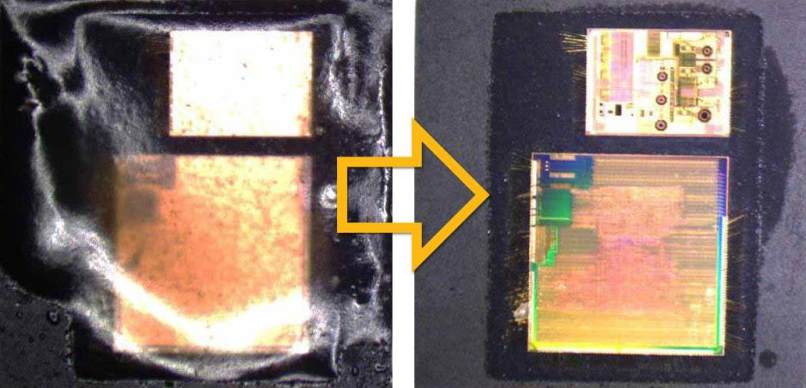

Recover MCU ATtiny88A Program from secured flash memory, unlock microcontroller attiny88a security fuse bit by focus ion beam skill and read the firmware from microprocessor attiny88a memory;

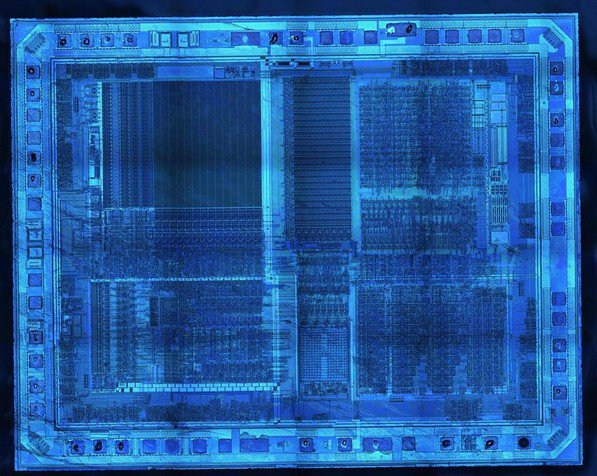

The ATtiny48/88 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny48/88 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle if Reverse engineering pic18f248 MCU.

The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers. The ATtiny48/88 provides the following features: 4/8K bytes of In-System Programmable Flash, 64/64 bytes EEPROM, 256/512 bytes SRAM, 24 general purpose I/O lines (28 I/Os in 32-lead TQFP and 32-pad QFN/MLF packages).

32 general purpose working registers, two flexible Timer/Counters with compare modes, internal and external interrupts, a byte-oriented 2-wire serial interface, an SPI serial port, a 6-channel 10-bit ADC (8 channels in 32-lead TQFP and 32-pad QFN/MLF packages), a programmable Watchdog Timer with internal oscillator, and three software selectable power saving modes.

Idle mode stops the CPU while allowing Timer/Counters, 2-wire serial interface, SPI port, and interrupt system to continue functioning. Power-down mode saves the register contents but freezes the oscillator, disabling all other MCU functions until the next interrupt or hardware reset. ADC Noise Reduction mode stops the CPU and all I/O modules except ADC, and helps to minimize switching noise during ADC conversions.

The device is manufactured using Atmel’s high density non-volatile memory technology. The On-MCU ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an on-MCU boot program running on the AVR core.

The boot program can use any interface to download the application program in the Flash memory. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic MCU, the Atmel ATtiny48/88 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATtiny48/88 AVR is supported by a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators and evaluation kits. This documentation contains simple code examples that briefly show how to use various parts of the device.

These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”.

Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C. Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.