Archive for the ‘Recover Chip’ Category

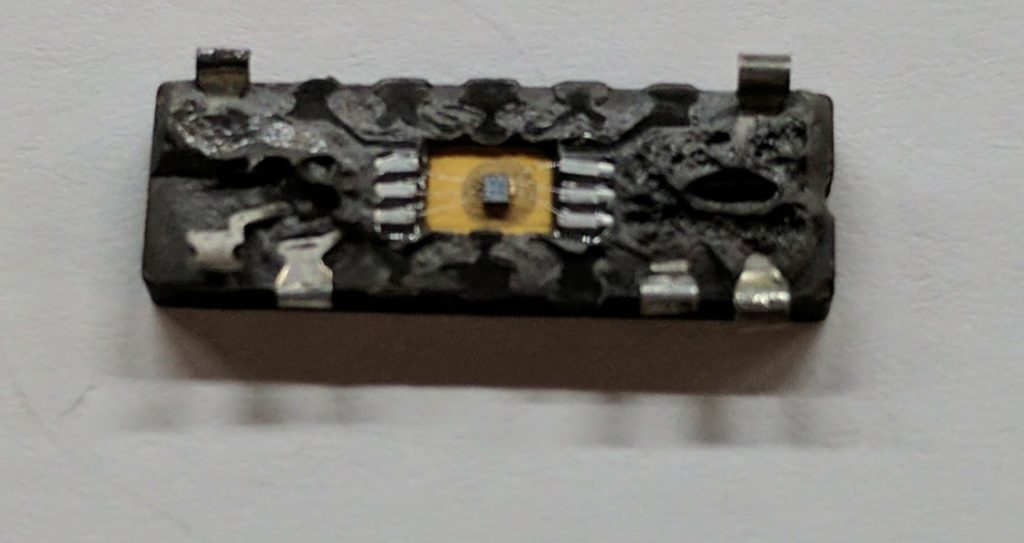

Decrypt Locked IC PIC16LF505 Program

Decrypt Locked IC PIC16LF505 Program

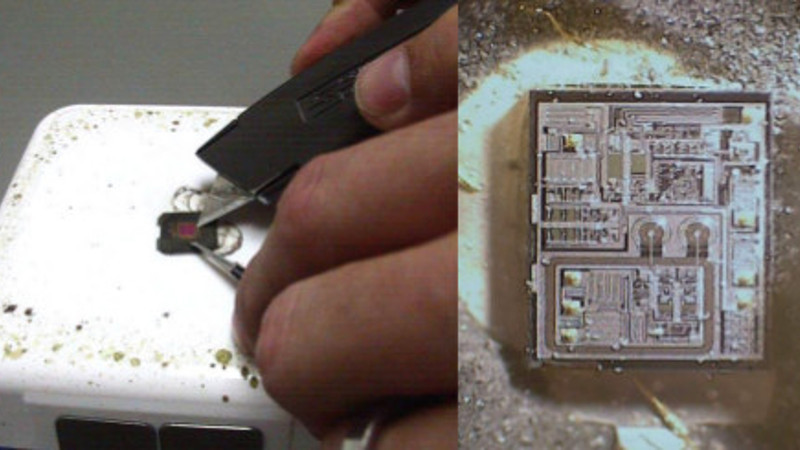

Decrypt Locked IC PIC16LF505 and extract MCU PIC16LF505 Program from flash memory and data from eeprom memory, use invasive Microcontroller unlocking skill to disable its security fuse bit;

The PIC16LF505 can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes:

In XT or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 8-2). The PIC16LF505 oscillator design requires the use of a parallel cut crystal.

Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT or LP modes, the device can have an external clock source drive the GP5/OSC1/CLKIN pin (Figure 8-3) before break mcu atmega128pa firmware.

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability.

A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance when break mcu atmega168a flash.

Figure 8-4 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires.

The 4.7 kΩ resistor provides the negative feedback for stability. The 10 kΩ potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

Recovery Chip PIC16F506 Firmware

Recovery Chip PIC16F506 Firmware

Recovery Chip PIC16F506 Firmware from microcontroller memory, crack PIC16F506 MCU flash and eeprom to readout PIC16F506 MCU code;

Random recovery operations allow the master to access any memory location in a random manner. To perform this type of recovery operation, first the word address must be set. This is done by sending the word address to the device as part of a write operation.

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16F506 family of microcontrollers has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection when Reverse engineering Chip pic18f248 binary firmware.

These features are:

Oscillator selection

Reset

– Power-On Reset (POR)

– Device Reset Timer (DRT)

– Wake-up from SLEEP on pin change

Watchdog Timer (WDT)

SLEEP

Code protection

ID locations

In-circuit Serial Programming

The PIC16F506 has a Watchdog Timer which can be shut off only through configuration bit WDTE. It runs off of its own RC oscillator for added reliability.

If using XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in reset until the crystal oscillator is stable.

If using INTRC or EXTRC there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power.

A set of configuration bits are used to select various options. The PIC16F506 configuration word consists of 12 bits. Configuration bits can be programmed to select various device configurations. Two bits are for the selection of the oscillator type, one bit is the Watchdog Timer enable bit, and one bit is the MCLR enable bit.

Decrypt IC PIC16F505 Flash

Decrypt IC PIC16F505 Flash

Decrypt IC PIC16F505 Flash memory content, and then extract chip PIC16F505 code out and decode PIC16F505 mcu embedded firmware;

Since the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput).

Once the stop condition for a write command has been issued from the master, the device initiates the internally timed write cycle. ACK polling can be initiated immediately if break microcontroller pic12f617 binary.

This involves the master sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned.

If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-6 for flow diagram after break IC pic12hv615 heximal.

It contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous read access was to address n, the next current address read operation would access data from address n + 1.

Upon receipt of the slave address with the R/W bit set to one, the device issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the device discontinues transmission.

Read operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read and sequential read before recover mcu pic16hv616 eeprom.

Retrieve IC PIC16LF57 Program

Retrieve IC PIC16LF57 Program

Retrieve IC PIC16LF57 Program from flash memory and eeprom memory, change the MCU PIC16LF57 status by unlock microcontroller‘s fuse bit and make PIC16LF57 processor copy;

The program for these functions is available on our website www.microchip.com. The program will be accessed by either including the source program FL51XINC.ASM or by linking FLASH5IX.ASM.

It is very important to check the return programs when using these calls, and retry the operation if unsuccessful. Unsuccessful return programs occur when the EE data memory is busy with the previous write, which can take up to 4 mS if break IC PIC16F884 code.

SDA is a bi-directional pin used to transfer addresses and data into and data out of the device. For normal data transfer SDA is allowed to change only during SCL low.

Changes during SCL high are reserved for indicating the START and STOP conditions. The EEPROM interface is a 2-wire bus protocol consisting of data (SDA) and a clock (SCL). Although these lines are mapped into the GPIO register, they are not accessible as external pins; only to the internal EEPROM peripheral after break IC PIC16F72A binary.

SDA and SCL operation is also slightly different than GPO-GP5 as listed below. Namely, to avoid program overhead in modifying the TRIS register, both SDA and SCL are always outputs. To read data from the EEPROM peripheral requires outputting a ‘1’ on SDA placing it in high-Z state, where only the internal 100K pull-up is active on the SDA line.

This program must reside in the lower half of a page. The program achieves it’s small size without additional calls through the use of a sequencing table. The table is a list of procedures that must be called in order. The table uses an ADDWF PCL,F instruction, effectively a computed goto, to sequence to the next procedure after Reverse eng microcontroller pic16c65b eeprom.

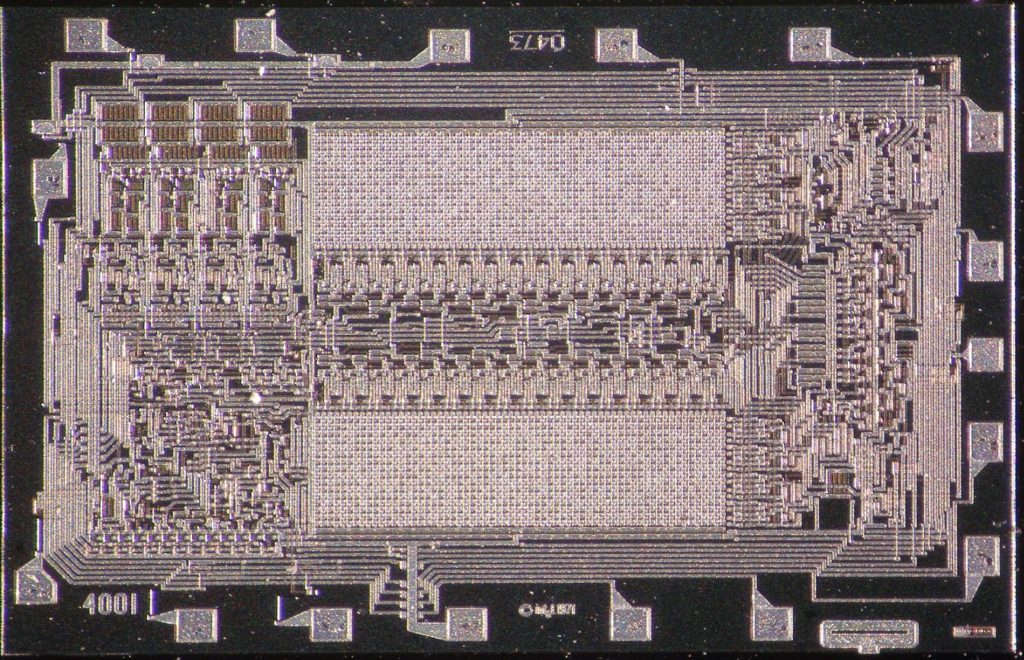

Decode Locked MCU PIC16F57 Heximal Data

Decode Locked MCU PIC16F57 Heximal Data

Decode Locked MCU PIC16F57 Heximal Data from eeprom memory, unlock microcontroller PIC16F57 security fuse bit and extract firmware out from microprocessor memory;

The Timer0 module has the following features:

8-bit timer/counter register, TMR0

– Readable and writable

8-bit heximal data programmable prescaler

Internal or external clock select

– Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler) if break ic pic16f917 hex.

If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI.

The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in heximal data by the control bit PSA (OPTION<3>) after recover mcu pic16f72 code.

Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,…, 1:256 are selectable. Section 6.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (TOSC) synchronization when recover mcu pic16f77 eeprom.

Also, there is a delay in the actual incrementing of Timer0 after synchronization. When no prescaler is used, the external clock input is the same as the prescaler output.

The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2TOSC (and a small RC delay of 20 ns) and low for at least 2TOSC (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

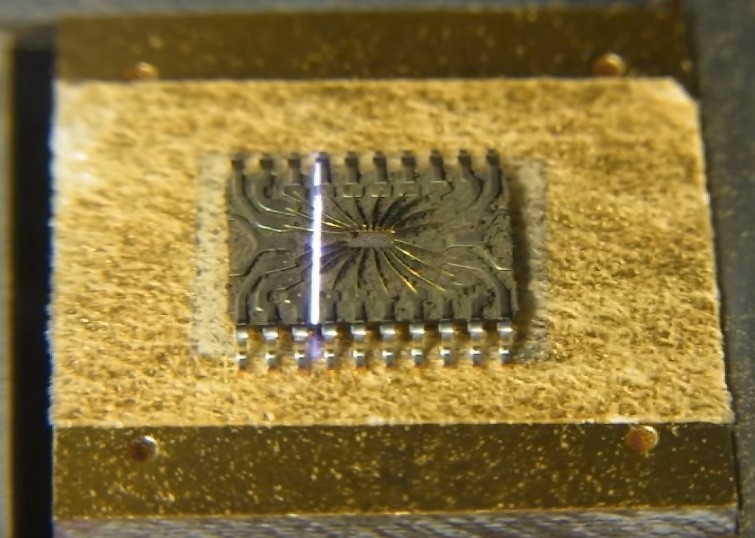

Reverse Engineering ATMEL AVR Chip ATmega32A Program File

Reverse Engineering ATMEL AVR Chip ATmega32A Program File

We can reverse engineering ATMEL AVR Chip ATMEGA32A program file, please view the ATMEL AVR Chip ATMEGA32A features for your reference:

The 9th bit of the program counter will be forced to a ‘0’ by any instruction that writes to the PC except for GOTO. See Section 4.7 “Program Counter”. When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is ‘1’ for a pin configured as input and is driven low by an external device, the data will be written back with a ‘0’.

The instruction TRIS f, where f = 6, causes the contents of the W register to be written to the tri-state latches of PORTB. A ‘1’ forces the pin to a high-impedance state and disables the output buffers.

If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

The PIC® ATMEL AVR Chips are supported with a full range of hardware and software development tools:

· Integrated Development Environment after Reverse Engineering ATMEL AVR Chip ATmega32A Program File.

– MPLAB® IDE Software

· Assemblers/Compilers/Linkers

– MPASMTM Assembler

– MPLAB C18 and MPLAB C30 C Compilers

– MPLINKTM Object Linker/MPLIBTM Object Librarian

– MPLAB ASM30 Assembler/Linker/Library

· Simulators

– MPLAB SIM Software Simulator

· Emulators

– MPLAB ICE 2000 In-Circuit Emulator

– MPLAB ICE 4000 In-Circuit Emulator

· In-Circuit Debugger

– MPLAB ICD 2

· Device Programmers

– PICSTART® Plus Development Programmer

– MPLAB PM3 Device Programmer

– PICkit™ 2 Development Programmer

· Low-Cost Demonstration and Development Boards and Evaluation Kits

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit ATMEL AVR Chip market. The MPLAB IDE is a Windows® operating system-based application that contains:

· A single graphical interface to all debugging tools after Reverse Engineering ATMEL AVR Chip ATmega32A Program File

– Simulator

– Programmer (sold separately)

– Emulator (sold separately)

– In-Circuit Debugger (sold separately)

· A full-featured editor with color-coded context

· A multiple project manager

· Customizable data windows with direct edit of contents

· High-level source code debugging

· Visual device initializer for easy register initialization

· Mouse over variable inspection

· Drag and drop variables from source to watch windows

· Extensive on-line help

· Integration of select third party tools, such as

HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

· Edit your source files (either assembly or C)

· One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

· Debug using:

– Source files (assembly or C)

– Mixed assembly and C

– Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power when Reverse Engineering Microcontroller.

Decode Atmel AVR Processor ATMEGA169P Locked Code

Decode Atmel AVR Processor ATMEGA169P Locked Code

We can decode Atmel AVR processor ATMEGA169P locked code, please view the Atmel AVR processor ATMEGA169P features for your reference:

The TO, PD, GPWUF and CWUF bits in the STATUS register can be tested to determine if a Reset condition has been caused by a power-up condition, a MCLR, Watchdog Timer (WDT) Reset, wake-up on comparator change or wake-up on pin change.

A Brown-out Reset is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown out.

A device may be powered down (Sleep) and later powered up (wake-up from Sleep). The Power-Down mode is entered by executing a SLEEP instruction before Decode Atmel AVR Processor ATMEGA169P Locked Code.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off.

The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

For lowest current consumption while powered down, the T0CKI input should be at VDD or VSS and the GP3/MCLR/VPP pin must be at a logic high level if MCLR is enabled.

The device can wake-up from Sleep through one of the following events:

An external Reset input on GP3/MCLR/VPP pin, when configured as MCLR. A Watchdog Timer time-out Reset (if WDT was enabled) before Decode Atmel AVR Processor ATMEGA169P Locked Code.

A change on input pin GP0, GP1 or GP3 when wake-up on change is enabled. wake-up on change is enabled. A comparator output change has occurred when wake-up on comparator change is enabled.

These events cause a device Reset. The TO, PD GPWUF and CWUF bits can be used to determine the cause of device Reset. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF bit indicates a change in state while in Sleep at pins GP0, GP1 or GP3 (since the last file or bit operation on GP port) when Decode Atmel AVR Processor ATMEGA169P Locked Code.

The CWUF bit indicates a change in the state while in Sleep of the comparator output.

Recover ATMEL AVR Chip ATtiny4313A Code

Recover ATMEL AVR Chip ATtiny4313A Code

We can Recover ATMEL AVR Chip ATTINY4313A Code, please view the ATMEL AVR Chip ATTINY4313A features for your reference:

The device is manufactured using Atmel’s high density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, or by a conventional non-volatile memory programmer.

By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATtiny4313a is a powerful ATMEL AVR Chip that provides a highly flexible and cost effective solution to many embedded control applications.

The ATtiny4313a AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-Circuit Emulators, and Evaluation kits if Recover ATMEL AVR Chip ATtiny4313A Code.

The ATtiny4313a differ only in memory sizes. Table 2-1 summarizes the different memory sizes for the two devices.

A comprehensive set of drivers, application notes, data sheets and descriptions on development tools are available for download at http://www.atmel.com/avr.

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation.

Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details when Recover ATMEL AVR Chip ATtiny4313A Code.

For I/O Registers located in the extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O if Recover ATMEL AVR Chip.

Typically, this means “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. Note that not all AVR devices include an extended I/O map before Recover MCU.

Reverse Engineering Encrypted AVR Chip ATtiny261 Software

Reverse Engineering Encrypted AVR Chip ATtiny261 Software

We can Reverse Engineering Encrypted AVR Chip ATtiny261 Software, please view the AVR Chip ATtiny261 features for your reference:

The ATtiny261 is a low-power CMOS 8-bit encrypted AVR chip based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle.

The ATtiny261 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle before Reverse Engineering Encrypted AVR Chip ATtiny261 Software.

The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC encrypted AVR chips.

The ATtiny261 provides the following features: 2/4/8K byte of In-System Programmable Flash, 128/256/512 bytes EEPROM, 128/256/512 bytes SRAM, 6 general purpose I/O lines, 32 general purpose working registers, one 8-bit Timer/Counter with compare modes.

One 8-bit high speed Timer/Counter, Universal Serial Interface, Internal and External Interrupts, a 4-channel, 10-bit ADC, a programmable Watchdog Timer with internal Oscillator.

And three software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counter, ADC, Analog Comparator, and Interrupt system to continue functioning before Reverse Engineering Encrypted AVR Chip ATtiny261 Software.

The Power-down mode saves the register contents, disabling all chip functions until the next Interrupt or Hardware Reset. The ADC Noise Reduction mode stops the CPU and all I/O modules except ADC, to minimize switching noise during ADC conversions.

The device is manufactured using Atmel’s high density non-volatile memory technology. The On-chip ISP Flash allows the Program memory to be re-programmed In-System through an SPI serial interface, by a conventional non-volatile memory programmer or by an On-chip boot code running on the AVR core when reverse engineering microcontroller.

Reverse Engineering IC ATmega1284PV Firmware

Reverse Engineering IC ATmega1284PV Firmware

Reverse Engineering IC ATmega1284PV structure to locate the security fuse bit, by unlocking MCU ATmega1284 memory and readout ATmega1284 IC Firmware.

Timer/Counter0 is a general purpose 8-bit Timer/Counter module, with two independent Output Compare Units, and with PWM support. It allows accurate program execution timing (event management) and wave generation. The main features are:

Two Independent Output Compare Units

Double Buffered Output Compare Registers

Clear Timer on Compare Match (Auto Reload)

Glitch Free, Phase Correct Pulse Width Modulator (PWM)

Variable PWM Period

Frequency Generator

Three Independent Interrupt Sources (TOV0, OCF0A, and OCF0B)

A simplified block diagram of the 8-bit Timer/Counter is shown in Figure 38. For the actual placement of I/O pins, refer to “Pinout ATmega640/1280/2560” on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the “8-bit Timer/Counter Register Description” on page 128.

The Timer/Counter (TCNT0) and Output Compare Registers (OCR0A and OCR0B) are 8-bit registers. Interrupt request (abbreviated to Int.Req. in the figure) signals are all visible in the Timer Interrupt Flag Register (TIFR0). All interrupts are individually masked with the Timer Interrupt Mask Register (TIMSK0). TIFR0 and TIMSK0 are not shown in the figure.

The Timer/Counter can be clocked internally, via the prescaler, or by an external clock source on the T0 pin. The Clock Select logic block controls which clock source and edge the Timer/Counter uses to increment (or decrement) its value when attack mcu pic16c558 program.

The Timer/Counter is inactive when no clock source is selected. The output from the Clock Select logic is referred to as the timer clock (clkT0).

The double buffered Output Compare Registers (OCR0A and OCR0B) are compared with the Timer/Counter value at all times. The result of the compare can be used by the Waveform Generator to generate a PWM or variable frequency output on the Output Compare pins (OC0A and OC0B). See “Output Compare Unit” on page 119. for details.

The Compare Match event will also set the Compare Flag (OCF0A or OCF0B) which can be used to generate an Output Compare interrupt request.