Archive for the ‘Recover Chip’ Category

Microcontroller W77E58 Embedded Firmware Restoration

Microcontroller W77E58 Embedded Firmware Restoration

When engineer encounter the PCB board which apply the microcontroller W77E58 which has been burned out, it needs to replace it with a fresh one, without the firmware the new MCU won’t work, in order to get Microcontroller W77E58 Embedded Firmware Restoration, we need to firstly understand the functional description of this microcontroller:

The W77E58 architecture consists of a core controller surrounded by various registers, five general purpose I/O ports, 128 bytes of RAM, two timer/counters, and a serial port. The processor supports 111 different opcodes and references both a 64K program address space and a 64K data storage space.

In order to be more suitable for I/O, an extra 4-bit bit-addressable port P4 and two external interrupt INT2 , INT3 has been added to either the PLCC or QFP 44 pin package when Microcontroller W77E58 Embedded Firmware Restoration. And description follows:

INT2 / INT3

Two additional external interrupts, INT2 and INT3, whose functions are similar to those of external interrupt 0 and 1 in the standard 80C52. The functions/status of these interrupts are determined/shown by the bits in the XICON (External Interrupt Control) register. The XICON register is bit-addressable but is not a standard register in the standard 80C52. Its address is at 0C0H. To set/clear bits in the XICON register, one can use the “SETB (/CLR) bit” instruction. For example, “SETB 0C2H” sets the EX2 bit of XICON.

XICON – external interrupt control (C0H)

PX3: External interrupt 3 priority high if set EX3: External interrupt 3 enable if set

IE3: If IT3 = 1, IE3 is set/cleared automatically by hardware when interrupt is detected/serviced IT3: External interrupt 3 is falling-edge/low-level triggered when this bit is set/cleared by software PX2: External interrupt 2 priority high if set after Microcontroller W77E58 Embedded Firmware Restoration

EX2: External interrupt 2 enable if set

IE2: If IT2 = 1, IE2 is set/cleared automatically by hardware when interrupt is detected/serviced IT2: External interrupt 2 is falling-edge/low-level triggered when this bit is set/cleared by software

Recover Winbond IC W78E065A Flash Program

Recover Winbond IC W78E065A Flash Program

Through the traditional power clitch method we can Recover Winbond IC W78E065A Flash Program, and then transfer it to other blank W78E065A processor which will perform the same functions as original if there is no bits are missing or error during the recovering process, now we need to have some general idea about how W78E065A microcontroller carry out the power management:

Idle Mode

The idle mode is entered by setting the IDL bit in the PCON register. In the idle mode, the internal clock to the processor is stopped. The peripherals and the interrupt logic continue to be clocked. The processor will exit idle mode when either an interrupt or a reset occurs after Recover Winbond IC W78E065A Flash Program.

Power-down Mode

When the PD bit of the PCON register is set, the processor enters the power-down mode. In this mode all of the clocks are stopped, including the oscillator. The only way to exit power-down mode is by a reset.

The external RESET signal is sampled at S5P2. To take effect, it must be held high for at least two machine cycles while the oscillator is running. An internal trigger circuit in the reset line is used to deglitch the reset line when the W78E51B is used with an external RC network.

The reset logic also has a special glitch removal circuit that ignores glitches on the reset line. During reset, the ports are initialized to FFH, the stack pointer to 07H, PCON (with the exception of bit 4) to 00H, and all of the other SFR registers except SBUF to 00H. SBUF is not reset.

Winbond Microcontroller W78E0516 Embedded Binary Recovering

Winbond Microcontroller W78E0516 Embedded Binary Recovering

In below article we are going to introduce watchdog timer which play an important role in the process of Winbond Microcontroller W78E0516 Embedded Binary Recovering:

As we all know that the Watchdog timer is a free-running timer which can be programmed by the user to serve as a system monitor, a time-base generator or an event timer. It is basically a set of dividers that divide the system clock. The divider output is selectable and determines the time-out interval.

When the time-out occurs a system reset can also be caused if it is enabled. The main use of the Watchdog timer is as a system monitor. This is important in real-time control applications. In case of power glitches or electro- magnetic interference, the processor may begin to execute errant code. If this is left unchecked the entire system may crash.

The watchdog time-out selection will result in different time-out values depending on the clock speed. The Watchdog timer will de disabled on reset. In general, software should restart the Watchdog timer to put it into a known state. The control bits that support the Watchdog timer are discussed below.

ENW : Enable watch-dog if set.

CLRW: Clear watch-dog timer and prescaler if set. This flag will be cleared automatically

WIDL : If this bit is set, watch-dog is enabled under IDLE mode. If cleared, watch-dog is disabled under IDLE mode. Default is cleared.

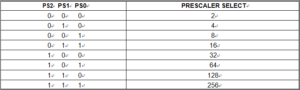

PS2, PS1, PS0: Watch-dog prescaler timer select. Prescaler is selected when set PS2~0 as follows:

The time-out period is obtained using the following equation:

OSC

´ 214 ´PRESCALER ´ 1000 ´ 12 mS

Before Watchdog time-out occurs, the program must clear the 14-bit timer by writing 1 to WDTC.6 (CLRW). After 1 is written to this bit, the 14-bit timer, prescaler and this bit will be reset on the next instruction cycle. The Watchdog timer is cleared on reset.

Recover Atmel AVR Controller ATmega48V Firmware

Recover Atmel AVR Controller ATmega48V Firmware

We can recover atmel avr controller ATMEGA48V firmware, please view the atmel avr controller ATMEGA48V features for your reference:

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Depending on the clock selection fuse settings, PB6 can be used as input to the inverting Oscillator amplifier and input to the internal clock operating circuit. Depending on the clock selection fuse settings, PB7 can be used as output from the inverting Oscillator amplifier.

If the Internal Calibrated RC Oscillator is used as chip clock source, PB7..6 is used as TOSC2..1 input for the Asynchronous Timer/Counter2 if the AS2 bit in ASSR is set before Recover Atmel AVR Controller ATmega48V Firmware.

Port C is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The PC5..0 output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

If the RSTDISBL Fuse is firmwaremed, PC6 is used as an I/O pin. Note that the electrical characteristics of PC6 differ from those of the other pins of Port C. If the RSTDISBL Fuse is unfirmwaremed, PC6 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running if Recover Atmel AVR Controller ATmega48V Firmware.

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

AVCC is the supply voltage pin for the A/D Converter, PC3:0, and ADC7:6. It should be externally connected to VCC, even if the ADC is not used. If the ADC is used, it should be connected to VCC through a low-pass filter. Note that PC6..4 use digital supply voltage, VCC before Recover Atmel AVR Controller ATmega48V Firmware.

In the TQFP and QFN/MLF package, ADC7:6 serve as analog inputs to the A/D converter. These pins are powered from the analog supply and serve as 10-bit ADC channels. The ATmega48V is a low-power CMOS 8-bit atmel avr controller based on the AVR enhanced RISC architecture.

By executing powerful instructions in a single clock cycle, the ATmega48/88/168 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed if RECOVER MCU.

Recover Encrypted Processor ATmega1284P Heximal

Recover Encrypted Processor ATmega1284P Heximal

We can recover encrypted processor ATMEGA1284P Heximal, please view the encrypted processor ATMEGA1284P features for your reference:

If the result is left-adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the data registers belongs to the same conversion when recover encrypted processor heximal.

Once ADCL is read, ADC access to data registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, neither register is updated and the result from the conversion is lost if recover encrypted processor heximal.

When ADCH is read, ADC access to the ADCH and ADCL registers is re-enabled. The ADC has its own interrupt, which can be triggered when a conversion completes. When ADC access to the data registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost before recover encrypted processor heximal.

The successive approximation circuitry requires an input clock frequency between 50 kHz and 200 kHz. Using a higher input frequency will affect the conversion accuracy, see “ADC Characteristics” on page 50 after recover encrypted processor heximal.

The ADC module contains a prescaler, which divides the system clock to an acceptable ADC clock frequency. The ADPSn bits in ADCSR are used to generate a proper ADC clock input frequency from any CK frequency above 100 kHz when recover encrypted processor heximal.

The prescaler starts counting from the moment the ADC is switched on by setting the ADEN bit in ADCSR. The prescaler keeps running for as long as the ADEN bit is set, and is continuously reset when ADEN is low if recover encrypted processor heximal.

When initiating a conversion by setting the ADSC bit in ADCSR, the conversion starts at the following rising edge of the ADC clock cycle. If differential channels are selected, the conversion will only start at every other rising edge of the ADC clock cycle after ADEN was set before recover encrypted processor heximal.

Recover Protected Microcontroller ATmega1284PA Heximal

Recover Protected Microcontroller ATmega1284PA Heximal

We can recover protected microcontroller ATMEGA1284PA heximal, please view the protected microcontroller ATMEGA1284PA features for your reference:

A normal conversion takes 13 ADC clock cycles. In certain situations, the ADC needs more clock cycles to perform initialization and minimize offset errors. These extended conversions take 25 ADC clock cycles and occur as the first conversion after one of the following events when recover protected microcontroller heximal:

the ADC is switched on (ADEN in ADCSR is set) the voltage reference source is changed (the REFS1..0 bits in ADMUX change value) a differential channel is selected (MUX2 in ADMUX is “1”) if recover protected microcontroller heximal.

Note that subsequent conversions on the same channel are not extended conversions.

The actual sample-and-hold takes place 1.5 ADC clock cycles after the start of a normal conversion and 13.5 ADC clock cycles after the start of an extended conversion. When a conversion is complete, the result is written to the ADC data registers, and ADIF is set before recover protected microcontroller heximal.

In Single Conversion mode, ADSC is cleared simultaneously. The software may then set ADSC again, and a new conversion will be initiated on the first rising ADC clock edge after recover protected microcontroller heximal.

In Free Running mode, a new conversion will be started immediately after the conversion completes while ADSC remains high. Using Free Running mode and an ADC clock frequency of 200 kHz gives the lowest conversion time, 65 µs, equivalent to 15 kSPS when recover protected microcontroller heximal.

For a summary of conversion times, see Table 18. The ADC features a noise canceler that enables conversion during ADC Noise Reduction mode (see “Sleep Modes” on page 23) to reduce noise induced from the CPU core and other I/O peripherals if recover protected microcontroller heximal.

If other I/O peripherals must be active during conversion, this mode works equivalently for Idle mode. To make use of this feature, the following procedure should be used before recover protected microcontroller heximal:

1. Make sure that the ADC is enabled and is not busy converting. Single Conversion mode must be selected and the ADC conversion complete interrupt must be enabled.

ADEN = 1

ADSC = 0

ADFR = 0

ADIE = 1

2. Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion once the CPU has been halted.

3. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the protected microcontroller and execute the ADC conversion complete interrupt routine after recover protected microcontroller heximal.

Decrypt Locked Microcontroller PIC24FJ16GA002 Software

Decrypt Locked Microcontroller PIC24FJ16GA002 Software

We can decrypt locked Microcontroller PIC24FJ16GA002 software, please view the locked Microcontroller PIC24FJ16GA002 features for your reference:

If the result is left-adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the data registers belongs to the same conversion.

Once ADCL is read, ADC access to data registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, neither register is updated and the result from the conversion is lost.

When ADCH is read, ADC access to the ADCH and ADCL registers is re-enabled. The ADC has its own interrupt, which can be triggered when a conversion completes before decrypt locked Microcontroller PIC24FJ16GA002 software.

When ADC access to the data registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost. The successive approximation circuitry requires an input clock frequency between 50 kHz and 200 kHz.

Using a higher input frequency will affect the conversion accuracy, see “ADC Characteristics” on page 50. The ADC module contains a prescaler, which divides the system clock to an acceptable ADC clock frequency.

The ADPSn bits in ADCSR are used to generate a proper ADC clock input frequency from any CK frequency above 100 kHz. The prescaler starts counting from the moment the ADC is switched on by setting the ADEN bit in ADCSR if decrypt locked Microcontroller PIC24FJ16GA002 software.

The prescaler keeps running for as long as the ADEN bit is set, and is continuously reset when ADEN is low. When initiating a conversion by setting the ADSC bit in ADCSR, the conversion starts at the following rising edge of the ADC clock cycle.

If differential channels are selected, the conversion will only start at every other rising edge of the ADC clock cycle after ADEN was set after RECOVER MCU.

Recover Microcontroller ATmega169PV Heximal

Recover Microcontroller ATmega169PV Heximal

We can recover Microcontroller ATmega169PV heximal, please view the Microcontroller ATmega169PV features for your reference:

Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

MOV @R0, #data Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space if Recover Microcontroller ATMEGA169PV Heximal.

The programmable Watchdog Timer (WDT) operates from an independent oscillator. The prescaler bits, PS0, PS1 and PS2 in SFR WCON are used to set the period of the Watchdog Timer from 16 ms to 2048 ms.

The available timer periods are shown in the following table and the actual timer periods (at VCC = 5V) are within ±30% of the nominal. The WDT is disabled by Power-on Reset and during Power Down.

It is enabled by setting the WDTEN bit in SFR WCON (address = 96H). The WDT is reset by setting the WDTRST bit in WCON. When the WDT times out without being reset or disabled, an internal RST pulse is generated to reset the CPU before Recover Microcontroller ATMEGA169PV Heximal.

Timer 0 and Timer 1 in the ATMEGA169PV operate the same way as Timer 0 and Timer 1 in the ATMEGA169PV. For further information, see the October 1995 IC Data Book, page 2-45, section titled, “Timer/Counters.”

Timer 2 is a 16 bit Timer/Counter that can operate as either a timer or an event counter.

The type of operation is selected by bit C/T2 in the SFR T2CON (shown in Table 2). Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator.

The modes are selected by bits in T2CON, as shown in Table 8. Timer 2 consists of two 8-bit registers, TH2 and TL2.

In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency before Recover Microcontroller ATMEGA169PV Heximal.

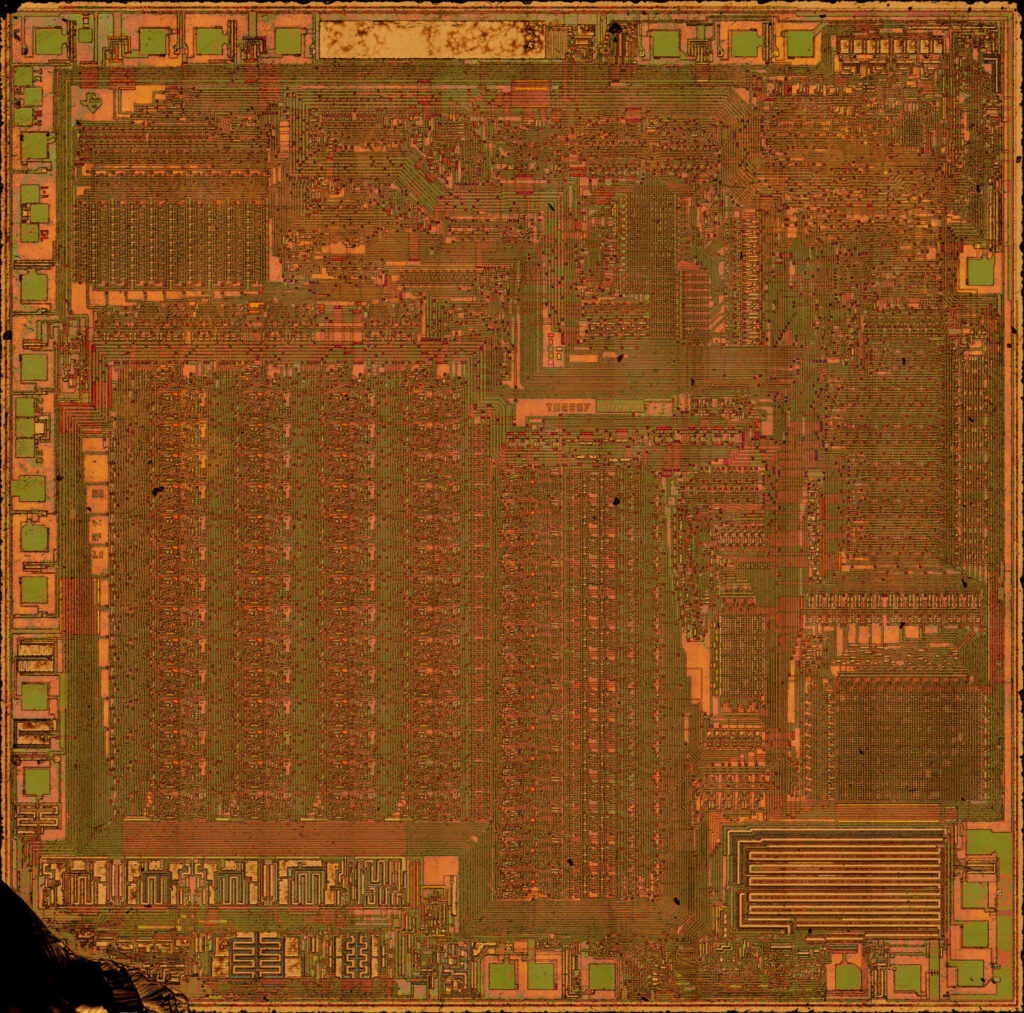

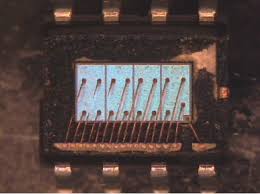

IC Flash Recovery

IC Flash Recovery

IC Flash Recovery is a process to extract code of MCU memory content, and copy the firmware to new Microcontroller for IC cloning;

IC Flash Recovery is a process to extract code of MCU memory content, and copy the firmware to new Microcontroller for IC cloning

Semi-invasive IC Flash Recovery, like invasive ic attack, require depackaging the chip to get access to the chip surface. But the passivation layer of the chip remains intact – semi-invasive ic break methods do not require electrical contact to the metal surface, so there is no mechanical damage to the silicon.

As invasive ic hacks are becoming constantly more demanding and expensive, with shrinking feature sizes and increasing device complexity, semi-invasive ic flash recovery become more attractive as they do not require very expensive tools and give results in a shorter time. Also, being applied to a whole transistor or even a group of transistors they are less critical to the small feature size of modern chips.

Decode MCU ATmega2560V Program

Decode MCU ATmega2560V Program

Decode MCU ATmega2560V Program from encrypted flash memory is a process of Microcontroller firmware extraction, reset the status of microprocessor ATmega2560V by unlocking;

We can decode mcu ATMEGA2560V program, please view the mcu ATMEGA2560V features for your reference:

The Code memory array can be programmed using the serial SPI bus while RST is pulled to VCC. The serial interface consists of pins SCK, MOSI (input) and MISO (output) when copy mcu at89c55wd binary.

After RST is set high, the Programming Enable instruction needs to be executed first before program/erase operations can be executed. An auto-erase cycle is built into the self-timed programming operation (in the serial mode ONLY) and there is no need to first execute the Chip Erase instruction unless any of the lock bits have been programmed.

The Chip Erase operation turns the content of every memory location in the Code array into FFH. The Code memory array has an address space of 0000H to 2FFFH.

Either an external system clock is supplied at pin XTAL1 or a crystal needs to be connected across pins XTAL1 and XTAL2. The maximum serial clock (SCK) frequency should be less than 1/40 of the crystal frequency. With a 24 MHz oscillator clock, the maximum SCK frequency is 600 kHz. To program and verify the AT89S53 in the serial programming mode, the following sequence is recommended:

Power-up sequence: Apply power between VCC and GND pins. Set RST pin to “H”. If a crystal is not connected across pins XTAL1 and XTAL2, apply a 3 MHz to 24 MHz clock to XTAL1 pin and wait for at least 10 milliseconds if attack mcu atmega162 flash program.

Enable serial programming by sending the Programming Enable serial instruction to pin MOSI/P1.5. The frequency of the shift clock supplied at pin SCK/P1.7 needs to be less than the CPU clock at XTAL1 divided by 40..

The Code array is programmed one byte at a time by supplying the address and data together with the appropriate Write instruction.

The selected memory location is first automatically erased before new data is written. The write cycle is self-timed and typically takes less than 2.5 ms at 5V. Any memory location can be verified by using the Read instruction which returns the content at the selected address at serial output MISO/P1.6 before attack microcontroller w77e058a40dl flash program.

At the end of a programming session, RST can be set low to commence normal operation. Power-off sequence (if needed): Set XTAL1 to “L” (if a crystal is not used). Set RST to “L”. Turn VCC power off.