Break STM32F038K6 Microcontroller Readout Protection

Break STM32F038K6 Microcontroller Readout Protection

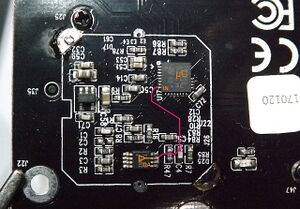

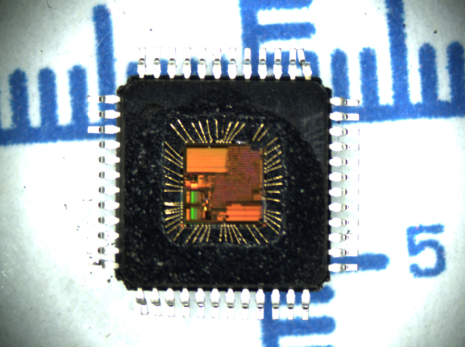

Break STM32F038K6 Microcontroller Readout Protection needs to use MCU cracking technique to disable the security fuse bit of microprocessor stm32f038k6, and then replicate flash data from mcu stm32f038k6;

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex®-M0) and 4

priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

The extended interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently.

сломать защиту считывания микроконтроллера STM32F038K6 необходимо использовать технику взлома MCU, чтобы отключить бит предохранителя микропроцессора STM32F038K6, а затем реплицировать данные флэш-памяти из MCU STM32F038K6;

A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 38 GPIOs can be connected to the 16 external interrupt lines.