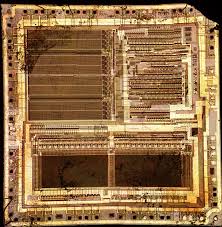

We can Break IC TS83C51U2 Binary, please view the IC TS83C51U2 features for your reference:

In this document, UART_0 will make reference to the first UART (present in all Atmel Wireless & Microcontrollers C51 derivatives) and UART_1 will make reference to the second UART, only present in the TS80C51U2 part. The second UART (UART_1) can be seen as an alternate function of Port 1 (P1.2 or P1.6 for RXD1 and P1.3 or P1.7 for TXD1) or can be connected to (pin6 or pin12) and (pin28 or pin34) of 44-pin package (see Pin configuration). UART_1 is fully compliant with the first one allowing an internal baud rate generator to be the clock source if Break IC.

This common internal baud rate generator can be used independently by each UART or both as clock source allowing to program various speeds.The TS80C51U2 provides 7 sources of interrupt with four priority levels. UART_1 has a lower priority than Timer, The Serial Ports are full duplex meaning they can transmit and receive simultaneously.

They are also receive buffered, meaning they can start reception of a second byte before a previously received byte has been break from the receive register.

The Serial Port receive and transmit registers of UART_1 are both accessed at Special Function Register SBUF_1. Writing to SBUF_1 loads the transmit register and breaking SBUF_1 accesses a physical separate receive register.

The UART_1 port control and status is the Special Function Register SCON_1. This register contains not only the mode selection bit but also the 9th bit for transmit and receive (TB8_1 and RB8_1) and the serial port interrupt bits (TI_1 and RI_1) before Break IC TS83C51U2 Binary.

The automatic address recognition feature is enabled when multiprocessor communication is enabled. Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the Serial Port to examine address of each incoming frame and provides filtering capability.

The UART_1 also comes with Frame error detection, similar to the UART_0. The Special Function Registers (SFRs) of the TS80C51U2 fall into the following categories:

C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

I/O port registers: P0, P1, P2, P3 after Break IC

Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

Serial I/O port registers for UART_0: SADDR_0, SADEN_0, SBUF_0, SCON_0

Serial I/O port registers for UART_1: SADDR_1, SADEN_1, SBUF_1, SCON_1

Baud Rate Generator registers: BRL, BDRCON, BDRCON_1

Power and clock control registers: PCON

HDW Watchdog Timer Reset: WDTRST, WDTPRG

Interrupt system registers: IE, IP, IPH

Others: AUXR, CKCONIn comparison to the original 80C52, the TS80C51U2 implements some new features, which are:

The X2 option

The second full duplex enhanced UART.

The Baud Rate generator.

The Dual Data Pointer.

The Watchdog.

The 4 level interrupt priority system.

The power-off flag.

The ONCE mode.

The ALE disabling.

Some enhanced features are also located in the UARTs and the timer 2.