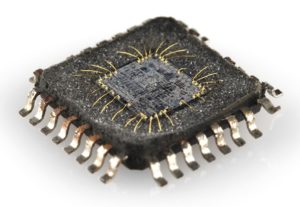

We can Break IC SN8P2606 Binary, please view the IC SN8P2606 features for your reference:

The power on reset depend no LVD operation for most power-up situations. The power supplying to system is a rising curve and needs some time to achieve the normal voltage. Power on reset sequence is as following:

Power-up: System detects the power voltage up and waits for power stable.

External reset (only external reset pin enable): System checks external reset pin status. If external reset pin is not high level, the system keeps reset status and waits external reset pin released if Break IC SN8P2606 Binary.

System initialization: All system registers is set as initial conditions and system is ready.

Oscillator warm up: Oscillator operation is successfully and supply to system clock.

Program executing: Power on sequence is finished and program executes from ORG 0.

Watchdog reset is a system protection. In normal condition, system works well and clears watchdog timer by program.

Under error condition, system is in unknown situation and watchdog can’t be clear by program before watchdog timer overflow. Watchdog timer overflow occurs and the system is reset. After watchdog reset, the system restarts and returns normal mode. Watchdog reset sequence is as following.

Watchdog timer status: System checks watchdog timer overflow status. If watchdog timer overflow occurs, the system is reset before Break IC SN8P2606 Binary.

System initialization: All system registers is set as initial conditions and system is ready.

Oscillator warm up: Oscillator operation is successfully and supply to system clock.

Program executing: Power on sequence is finished and program executes from ORG 0 when Break IC SN8P2606 Binary.

Watchdog reset is a system protection. In normal condition, system works well and clears watchdog timer by program.

Under error condition, system is in unknown situation and watchdog can’t be clear by program before watchdog timer overflow. Watchdog timer overflow occurs and the system is reset. After watchdog reset, the system restarts and returns normal mode. Watchdog reset sequence is as following.

Watchdog timer status: System checks watchdog timer overflow status. If watchdog timer overflow occurs, the system is reset.

System initialization: All system registers is set as initial conditions and system is ready.

Oscillator warm up: Oscillator operation is successfully and supply to system clock.

Program executing: Power on sequence is finished and program executes from ORG 0. Watchdog timer application note is as following after Break IC SN8P2606 Binary.

Before clearing watchdog timer, check I/O status and check RAM contents can improve system error. Don’t clear watchdog timer in interrupt vector and interrupt service routine. That can improve main routine fail. Clearing watchdog timer program is only at one part of the program. This way is the best structure to enhance the watchdog timer function.