Break IC ATtiny85V Software

Break IC ATtiny85V Software

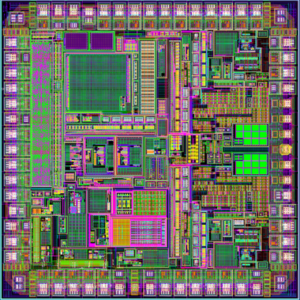

Break IC ATtiny85V can help engineer to readout the embedded firmware from mcu attiny85v flash and eeprom memory, fuse bit of microcontroller attiny85v can be cracked;

Break IC ATtiny85V can help engineer to readout the embedded firmware from mcu attiny85v flash and eeprom memory, fuse bit of microcontroller attiny85v can be cracked

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-IC oscillator, as shown in Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

In idle mode, the CPU puts itself to sleep while all the on-IC peripherals remain active. The mode is invoked by software. The content of the on-IC RAM and all the special functions registers remain unchanged during Break mcu pic16f876 memory.

Figure 2. External Clock Drive Configuration mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset before Break IC. It should be noted that when idle is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-IC hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited.

To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory. In the power down mode the oscillator is stopped, and the instruction that invokes power down is the last instruction executed. The on-IC RAM and Special Function Registers retain their values until the power down mode is terminated.

The only exit from power down is a hardware reset. Reset redefines the SFRs but does not change the on-IC RAM. The reset should not be activated before VCC is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize if Break IC.