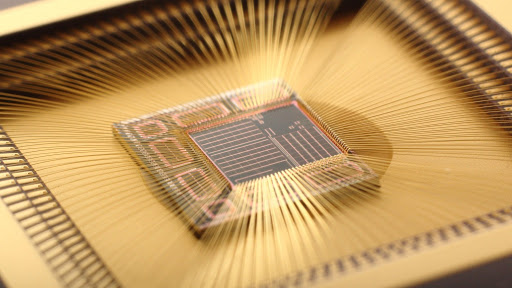

Break IC ATmega128A Eprom

Break IC ATmega128A Eprom

Break IC ATmega128A Eprom memory and restore the embedded firmware from atmega128a flash memory, the firmware of atmega128a microcontroller can be readout directly after reset the status.

The Atmel QTouch Library provides a simple to use solution to realize touch sensitive interfaces on most Atmel AVR microcontrollers. The QTouch Library includes support for the QTouch and QMatrix acquisition methods.

Touch sensing can be added to any application by linking the appropriate Atmel QTouch Library for the AVR Microcontroller. This is done by using a simple set of APIs to define the touch channels and sensors, and then calling the touch sensing API’s to retrieve the channel information and determine the touch sensor states if reverse engineering microcontroller attiny461.

The QTouch Library is FREE and downloadable from the Atmel website at the following location: www.atmel.com/qtouchlibrary. For implementation details and other information, refer to the Atmel QTouch Library User Guide – also available for download from the Atmel website.

First Analog Comparator conversion may be delayed Interrupts may be lost when writing the timer registers in the asynchronous timer Stabilizing time needed when changing XDIV Register

Stabilizing time needed when changing OSCCAL Register

IDCODE masks data from TDI input

Breaking EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request

First Analog Comparator conversion may be delayed

If the device is powered by a slow rising VCC, the first Analog Comparator conversion will take longer than expected on some devices if reverse engineering microcontroller atmega640.

Problem Fix/Workaround

When the device has been powered or reset, disable then enable theAnalog Comparator before the first conversion.

Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

Problem Fix/Workaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

Stabilizing time needed when changing XDIV Register

After increasing the source clock frequency more than 2% with settings in the XDIV register, the device may execute some of the subsequent instructions incorrectly when Break IC.

Problem Fix / Workaround

The NOP instruction will always be executed correctly also right after a frequency change.

Thus, the next 8 instructions after the change should be NOP instructions. To ensure this, follow this procedure:

1.Clear the I bit in the SREG Register.

2.Set the new pre-scaling factor in XDIV register.

3.Execute 8 NOP instructions

4.Set the I bit in SREG

This will ensure that all subsequent instructions will execute correctly.

Assembly Code Example:

Stabilizing time needed when changing OSCCAL Register before Break IC

After increasing the source clock frequency more than 2% with settings in the OSCCAL register, the device may execute some of the subsequent instructions incorrectly.

Problem Fix / Workaround

The behavior follows errata number 3., and the same Fix / Workaround is applicable on this errata.

IDCODE masks data from TDI input

The JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.

Problem Fix / Workaround

If ATmega128 is the only device in the scan chain, the problem is not visible.

Select the Device ID Register of the ATmega128 by issuing the IDCODE instruction or by entering the Test-Logic-Reset state of the TAP controller to break out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYPASS instruction to the ATmega128 while breaking the Device ID Registers of preceding devices of the boundary scan chain.

If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the ATmega128 must be the fist device in the chain.

Breaking EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request.

Breaking EEPROM by using the ST or STS command to set the EERE bit in the EECR register triggers an unexpected EEPROM interrupt request.

Problem Fix / Workaround

Always use OUT or SBI to set EERE in EECR.