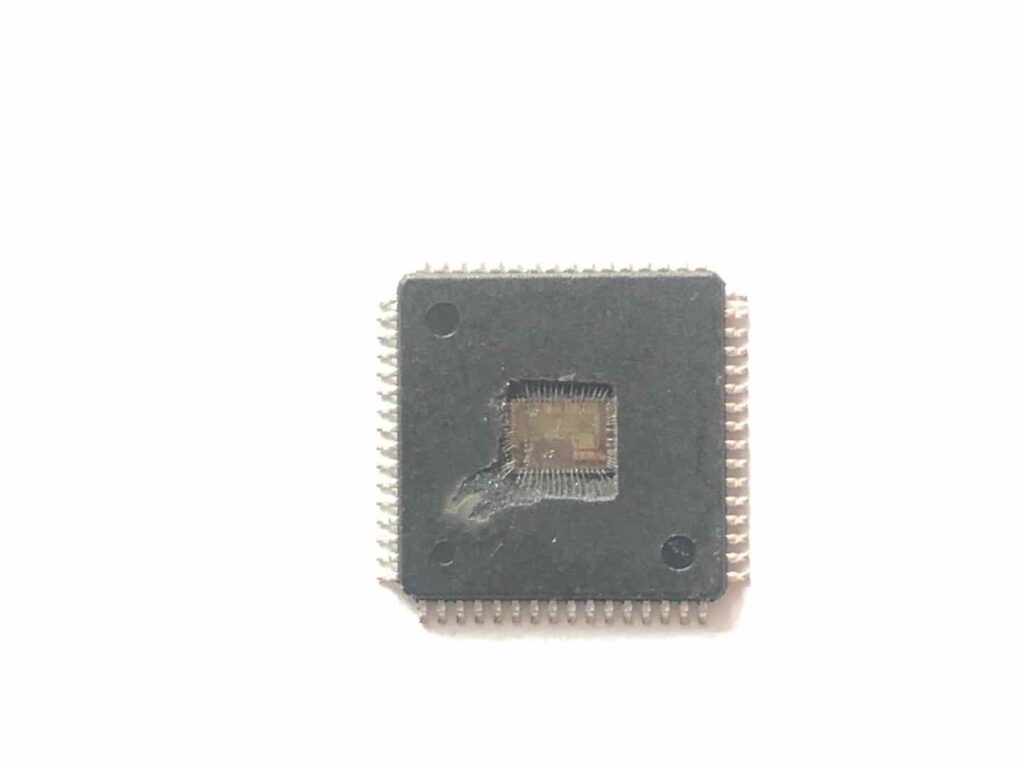

Automobile Microprocessor SPC56EL64 Embedded Program Extraction

Automobile Microprocessor SPC56EL64 Embedded Program Extraction

Automobile Microprocessor SPC56EL64 Embedded Program Extraction is a process to extract flash heximal file from MCU flash memory after crack microcontroller spc56el64 protective system;

The following list summarizes the system clock and clock generation on this device:

- Lock status continuously monitored by lock detect circuitry

- Loss-of-clock (LOC) detection for reference and feedback clocks

- On-chip loop filter (for improved electromagnetic interference performance and fewer external components required)

- Programmable output clock divider of system clock (¸1, ¸2, ¸4, ¸8)

- FlexPWM module and as many as three eTimer modules running on an auxiliary clock independent from system clock (with max frequency 120 MHz)

- On-chip crystal oscillator with automatic level control

- Dedicated internal 16 MHz internal RC oscillator for rapid start-up

- Supports automated frequency trimming by hardware during device startup and by user application

- Auxiliary clock domain for motor control periphery (FlexPWM, eTimer, CTU, ADC, and SWG)

Each device has two FMPLLs.

otomobil mikroişlemcisi SPC56EL64 gömülü program Ekstraksiyon mikrodenetleyici spc56el64 koruyucu sistem çatlak sonra MCU flash bellekten flash onaltılık dosya ayıklamak için bir işlemdir

Each FMPLL allows the user to generate high speed system clocks starting from a minimum reference of 4 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock by reading spc56el54l3 mcu flash memory firmware. The FMPLL multiplication factor, output clock divider ratio are all software configurable. The FMPLLs have the following major features:

- Input frequency: 4–40 MHz continuous range (limited by the crystal oscillator)

- Voltage controlled oscillator (VCO) range: 256–512 MHz

- Frequency modulation via software control to reduce and control emission peaks

- Modulation depth ±2% if centered or 0% to –4% if downshifted via software control register

- Modulation frequency: triangular modulation with 25 KHz nominal rate

- Option to switch modulation on and off via software interface

- Reduced frequency divider (RFD) for reduced frequency operation without re-lock after duplicating microprocessor spc56el70l5 flash program

- 3 modes of operation

- Bypass mode

- Normal FMPLL mode with crystal reference (default)

- Normal FMPLL mode with external reference

- Lock monitor circuitry with lock status

- Loss-of-lock detection for reference and feedback clocks

- Self-clocked mode (SCM) operation

- On-chip loop filter

- Auxiliary FMPLL

- Used for FlexRay due to precise symbol rate requirement by the protocol

- Used for motor control periphery and connected IP (A/D digital interface CTU) to allow independent frequencies of operation for PWM and timers and jitter-free control