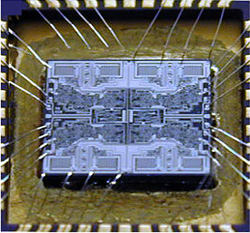

Attack Chip dsPIC33FJ256GP506A and compromise Microcontroller dsPIC33FJ256GP506 tamper resistance system, readout MCU software from dsPIC33FJ256 flash and eeprom memory

Attack Chip dsPIC33FJ256GP506A and compromise Microcontroller dsPIC33FJ256GP506 tamper resistance system, readout MCU software from dsPIC33FJ256 flash and eeprom memory;

Operating Conditions

· 3.0V to 3.6V, -40ºC to +150ºC, DC to 20 MIPS

· 3.0V to 3.6V, -40ºC to +125ºC, DC to 40 MIPS

Core: 16-bit dsPIC33F CPU

Timers/Output Compare/Input Capture

· Up to nine 16-bit timers/counters. Can pair up to make four 32-bit timers;

· Eight Output Compare modules configurable as timers/counters;

Code-efficient (C and Assembly) architecture

Two 40-bit wide accumulators

Single-cycle (MAC/MPY) with dual data fetch

Single-cycle mixed-sign MUL plus hardware divide

· Eight Input Capture modules

Communication Interfaces

· Two UART modules (10 Mbps)

– With support for LIN 2.0 protocols and IrDA®

· Two 4-wire SPI modules (15 Mbps)

Clock Management

· Up to two I2C™ modules (up to 1 Mbaud) with ±2% internal oscillator

Programmable PLLs and oscillator clock sources

Fail-Safe Clock Monitor (FSCM)

Independent Watchdog Timer (WDT)

Fast wake-up and start-up

SMBus support

· Up to two Enhanced CAN (ECAN) modules (1 Mbaud) with 2.0B support

· Data Converter Interface (DCI) module with I2S codec support

Power Management

· Low-power management modes (Sleep, Idle, Doze)

· Integrated Power-on Reset and Brown-out Reset

· 2.1 mA/MHz dynamic current (typical)

· 50 μA IPD current (typical)

Advanced Analog Features

· Two ADC modules:

– Configurable as 10-bit, 1.1 Msps with four S&H or 12-bit, 500 ksps with one S&H

– 18 analog inputs on 64-pin devices and up to 32 analog inputs on 100-pin devices

· Flexible and independent ADC trigger sources

Input/Output

· Sink/Source up to 10 mA (pin specific) for standard VOH/VOL, up to 16 mA (pin specific) for non-standard VOH1

· 5V-tolerant pins

· Selectable open drain, pull-ups, and pull-downs

· Up to 5 mA overvoltage clamp current

· External interrupts on all I/O pins

Qualification and Class B Support

· AEC-Q100 REVG (Grade 1 -40ºC to +125ºC)

· AEC-Q100 REVG (Grade 0 -40ºC to +150ºC)

· Class B Safety Library, IEC 60730

Debugger Development Support

Packages

In-circuit and in-application programming

Two program and two complex data breakpoints

IEEE 1149.2-compatible (JTAG) boundary scan

Trace and run-time watch