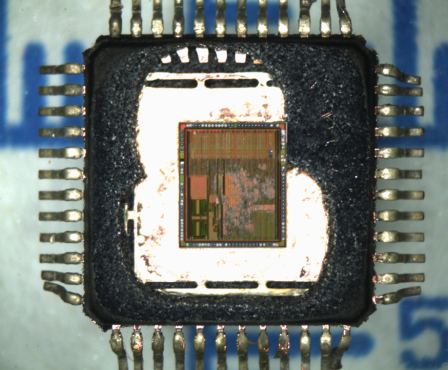

Restore Microchip PIC18F25K50 Processor Flash Heximal

Restore Microchip PIC18F25K50 Processor Flash Heximal

Restore Microchip PIC18F25K50 Processor Flash Heximal from its embedded flash memory, the tamper resistance system of PIC18F25K50 Microcontroller will be cracked, and then copy flash heximal from pic18f25k50 microprocessor flash memory;

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

Upon a wake from a Sleep event, the core will wait for a combination of three conditions before beginning execution. The conditions are:

PFM Ready

COSC-Selected Oscillator Ready

BOR Ready (unless BOR is disabled)

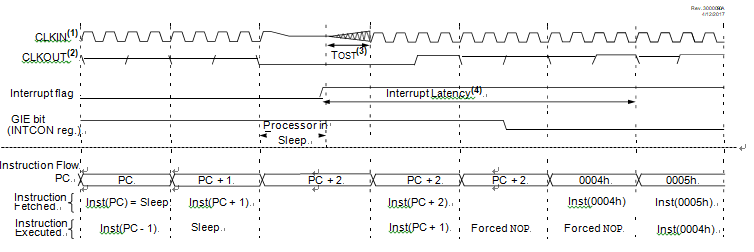

When global interrupts are disabled (GIE cleared) and any interrupt source, with the exception of the clock switch interrupt to break PIC18F25K20 microchip controller locked memory, has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

restaurar Microchip PIC18F25K50 procesador flash heximal de su memoria flash integrada, el sistema de resistencia a la manipulación de PIC18F25K50 Microcontrolador será agrietado, y luego copiar flash heximal de pic18f25k50 microprocesador de memoria flash

If the interrupt occurs before the execution of a SLEEP instruction

SLEEP instruction will execute as a NOP

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.