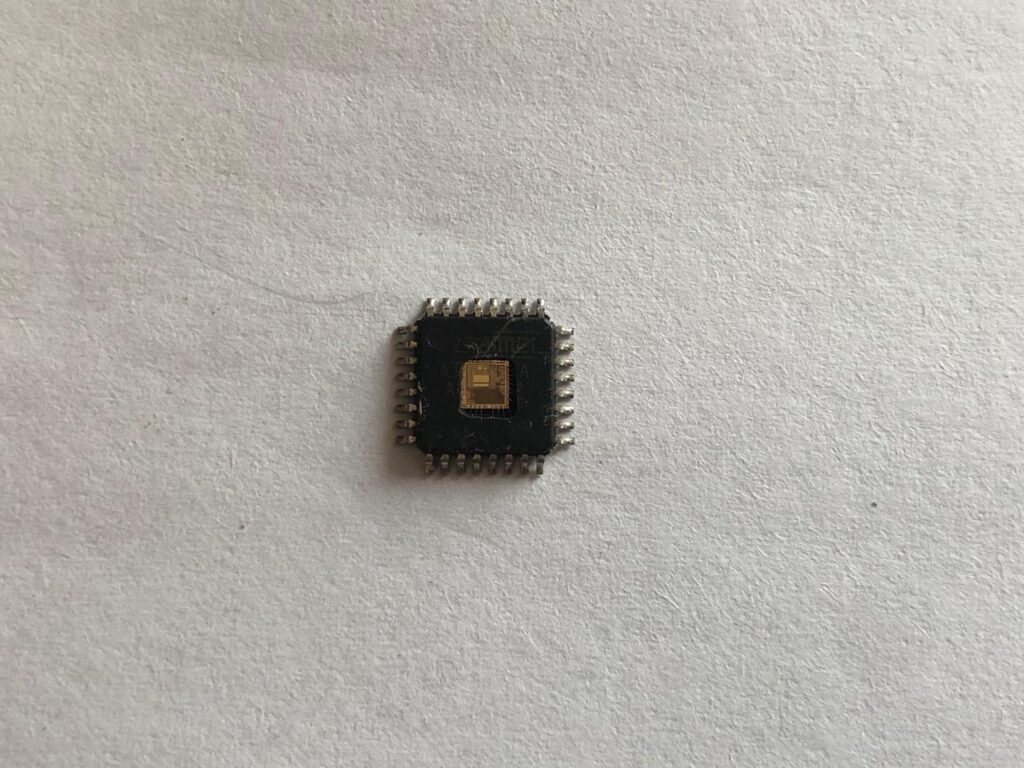

Altera CPLD EPM7064AETC100 Chip Protection Breaking

Altera CPLD EPM7064AETC100 Chip Protection Breaking

Altera CPLD EPM7064AETC100 Chip Protection Breaking needs to unlock epm7064aetc100 security fuse bit by focus ion beam and then copy embedded firmware from eeprom memory of cpld chip;

Bus-friendly architecture, including programmable slew-rate control

Open-drain output option

Programmable macrocell registers with individual clear, preset, clock, and clock enable controls

Programmable power-up states for macrocell registers in MAX 7000AE devices

Altera CPLD EPM7064AETC100 захист мікросхеми від злому повинен розблокувати запобіжник безпеки epm7064aetc100 біт за променем focus ion beam, а потім скопіювати вбудовану прошивку з пам’яті eeprom чіпа cpld;

Programmable power-saving mode for 50% or greater power reduction in each macrocell

Configurable expander product-term distribution, allowing up to 32 product terms per macrocell

Programmable security bit for protection of proprietary designs 6 to 10 pin- or logic-driven output enable signals

Two global clock signals with optional inversion

Enhanced interconnect resources for improved routability

Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

Programmable output slew-rate control from Crack PLD IC Altera EPM7064AETC100-4N

Programmable ground pins

Software design support and automatic place-and-route provided by Altera’s development systems for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest.

Altera CPLD EPM7064AETC100 ruperea protecției cipului trebuie să deblocheze siguranța de securitate epm7064aetc100 bit cu fascicul de ioni de focalizare și apoi să copieze firmware-ul încorporat din memoria eeprom a cipului CPLD;

Programming support with Altera’s Master Programming Unit (MPU), MasterBlasterTM serial/universal serial bus (USB) communications cable, ByteBlasterMVTM parallel port download cable, and BitBlasterTM serial download cable, as well as programming hardware from third-party manufacturers and any JamTM STAPL File (.jam), Jam Byte-Code File (.jbc), or Serial Vector Format File (.svf) capable in-circuit tester when recover altera cpld epm7064aetc100 software.