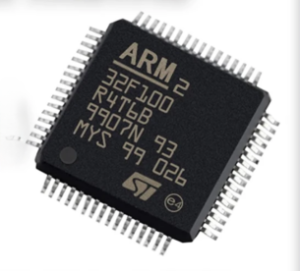

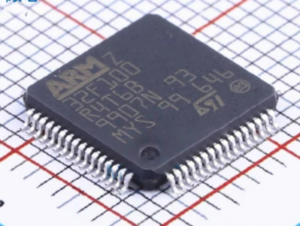

Recover STMicro STM32F100R4 Processor Flash Source Code

Recover STMicro STM32F100R4 Processor Flash Source Code

Recover STMicro STM32F100R4 Processor Flash Source Code from locked flash memory, crack arm microcontroller stm32f100r4 tamper resistance system and readout embedded firmware from MCU;

The STM32F100R4 value line embeds a nested vectored interrupt controller able to handle up to 41 maskable interrupt channels (not including the 16 interrupt lines of Cortex™-M3) and 16 priority levels which will affect Crack STM32F100R4 ARM Microcontroller process.

Closely coupled NVIC gives low latency interrupt processing

Interrupt entry vector table address passed directly to the core

Closely coupled NVIC core interface

Allows early processing of interrupts

Processing of late arriving higher priority interrupts

Support for tail-chaining

Processor state automatically saved

Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

استعادة STMicro STM32F100R4 شفرة مصدر فلاش المعالجات الدقيقة من ذاكرة فلاش مقفلة ، متحكم ذراع الكراك STM32F100R4 نظام مقاومة العبث وقراءة البرامج الثابتة المضمنة من MCU ؛

The external interrupt/event controller consists of 18 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently to provide better support in the process of restoring arm microprocessor stm32f100r8 program file.

A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-24 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator.

लॉक ्ड फ्लैश मेमोरी से एसटीमाइक्रो STM32F100R4 माइक्रोप्रोसेसर फ्लैश सोर्स कोड पुनर्प्राप्त करें, टैम्पर प्रतिरोध प्रणाली के STM32F100R4 आर्म माइक्रोकंट्रोलर को क्रैक करें और एमसीयू से रीडआउट एम्बेडेड फर्मवेयर;

A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency to Break IC memory, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 24 MHz.