Attack Microchip PIC18F45K20 MCU Memory Protection

Attack Microchip PIC18F45K20 MCU Memory Protection

Attack Microchip PIC18F45K20 MCU Memory Protection and unlock microcontroller pic18f45k20 flash and eeprom memory, read embedded heximal from mcu with programmer;

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register.

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in Section 6.5 “Writing to Flash Program Memory”.

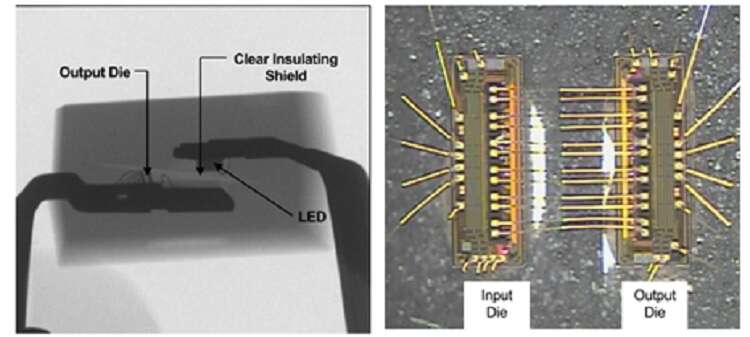

Figure 6-2 shows the operation of a table write with program memory and data RAM. Table operations work with byte entities. Tables contain- ing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned for pic18f43k20 flash memory breaking.

protezione della memoria MCU del microchip PIC18F45K20 protetta dall’attacco e sblocco protetto della memoria flash ed eeprom del microcontrollore PIC18F45K20, lettura dei dati esagonali incorporati o del codice sorgente binario dalla memoria flash crittografata PIC18F45K20 del microprocessore e dal firmware incorporato della memoria eeprom con programmatore;

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all ‘0’s.

The EEPGD control bit determines if the access will be a program or data EEPROM memory access. When EEPGD is clear, any subsequent operations will operate on the data EEPROM memory.

zabezpieczony przed atakiem mikrochip PIC18F45K20 ochrona pamięci MCU i odblokowanie chronionego mikrokontrolera PIC18F45K20 pamięć flash i eeprom, odczyt osadzonych danych szesnastkowych lub binarnego kodu źródłowego z zaszyfrowanej mikroprocesorem pamięci flash PIC18F45K20 i wbudowanego oprogramowania sprzętowego pamięci eeprom z programatorem;

When EEPGD is set, any subsequent operations will operate on the program memory. The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory/data EEPROM memory.

When CFGS is set, subsequent operations will operate on Configuration registers regardless of EEPGD (see Section 23.0“Special Features of the CPU”). When CFGS is clear, memory selection access is determined by EEPGD.