32 Bit Power Architecture MCU SPC56AP54L5 Flash Memory Recovery

32 Bit Power Architecture MCU SPC56AP54L5 Flash Memory Recovery

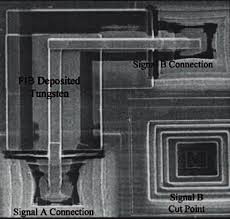

32 Bit Power Architecture MCU SPC56AP54L5 Flash Memory Recovery means embedded heximal will be readout from locked flash memory of microcontroller spc56ap54l5, original status of microprocessor SPC56AP54L5 can be unlocked by MCU cracking technique;

The e200z0h Power Architecture core provides the following features:

32-битная архитектура питания MCU SPC56AP54L5 восстановление флэш-памяти означает, что встроенный гекзимал будет считываться из заблокированной флэш-памяти микроконтроллера SPC56AP54L5, исходное состояние микропроцессора SPC56AP54L5 может быть разблокировано с помощью метода взлома MCU

- High performance e200z0 core processor for managing peripherals and interrupts

- Single issue 4-stage pipeline in-order execution 32-bit Power Architecture CPU

- Harvard architecture

- Variable length encoding (VLE), allowing mixed 16-bit and 32-bit instructions

- Results in smaller code size footprint

- Minimizes impact on performance

- Branch processing acceleration using lookahead instruction buffer

- Load/store unit in the process of cloning of stm microcontroller spc56el54l5 memory data

- 1-cycle load latency

- Misaligned access support

- No load-to-use pipeline bubbles

- Thirty-two 32-bit general purpose registers (GPRs)

- Separate instruction bus and load/store bus Harvard architecture

- Hardware vectored interrupt support

- Reservation instructions for implementing read-modify-write constructs

- Long cycle time instructions, except for guarded loads, do not increase interrupt latency

- Extensive system development support through Nexus debug port

- Non maskable Interrupt support