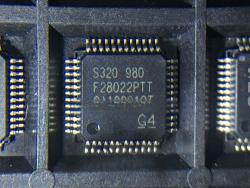

Reverse TMS320F28022 Microcontroller Locked Flash Memory

Reverse TMS320F28022 Microcontroller Locked Flash Memory

reverse engineering TMS320F28022PTT secured microcontroller locked flash memory after unlock MCU TMS320F28022PTT protection system and readout the embedded firmware of binary file or eeprom memory heximal data from original microprocessor TMS320F28022PTT;

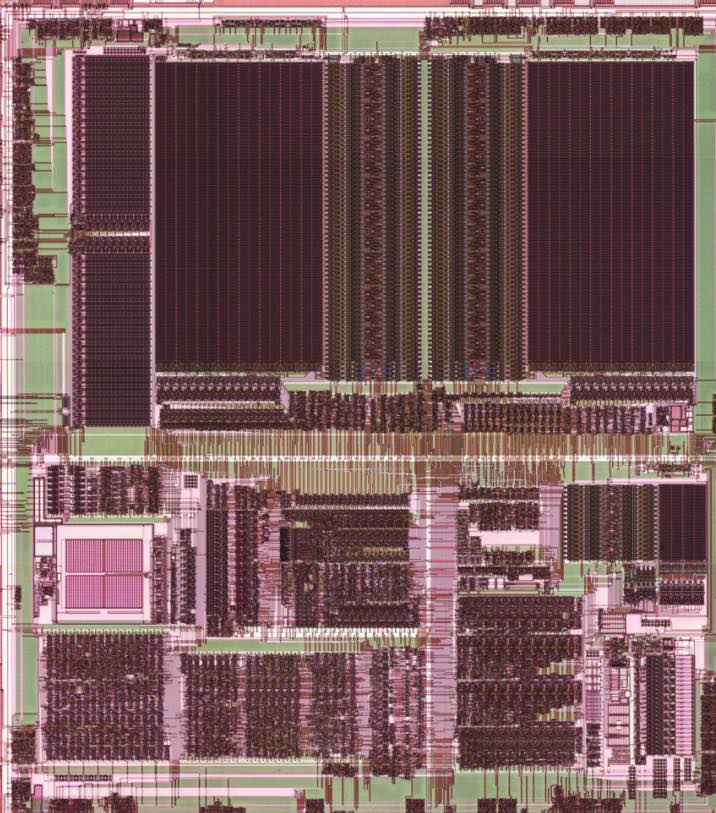

As with many DSP type devices, multiple busses are used to move data between the memories and peripherals and the CPU. The C28x memory bus architecture contains a program read bus, data read bus and data write bus. The program read bus consists of 22 address lines and 32 data lines.

ingeniería inversa TMS320F28022PTT microcontrolador asegurado memoria flash bloqueada después de desbloquear el sistema de protección MCU TMS320F28022PTT y leer el firmware integrado del archivo binario o datos heximales de la memoria eeprom del microprocesador original TMS320F28022PTT;

The data read and write busses consist of 32 address lines and 32 data lines each. The 32-bit-wide data busses enable single cycle 32-bit operations. The multiple bus architecture, commonly termed Harvard Bus, enables the C28x to fetch an instruction, read a data value and write a data value in a single cycle.

All peripherals and memories attached to the memory bus will prioritize memory accesses to reverse tms320f28016 flash code. Generally, the priority of memory bus accesses can be summarized as follows:

зваротная распрацоўка TMS320F28022PTT, абароненая флэш-памяць, заблакіраваная мікракантролерам, пасля разблакіроўкі MCU, сістэма абароны TMS320F28022PTT і счытванне ўбудаванай прашыўкі двайковага файла або памяці eeprom, шаснаццаткавыя дадзеныя з арыгінальнага мікрапрацэсара TMS320F28022PTT;

Highest:

Data Writes (Simultaneous data and program writes cannot occur on the memory bus.)

Program Writes (Simultaneous data and program writes cannot occur on the memory bus.)

Data Reads Program

(Simultaneous program reads and fetches cannot occur on the Reads memory bus.)

Lowest:

Fetches (Simultaneous program reads and fetches cannot occur on the memory bus.)

tersine mühendislik TMS320F28022PTT, MCU TMS320F28022PTT koruma sisteminin kilidini açtıktan ve orijinal mikroişlemci TMS320F28022PTT’den ikili dosya veya eeprom belleğinin onaltılık verilerinin yerleşik donanım yazılımını okuduktan sonra güvenli mikro denetleyici kilitli flash bellek;