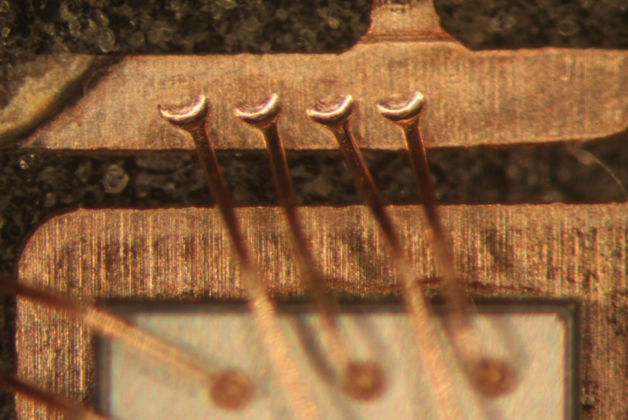

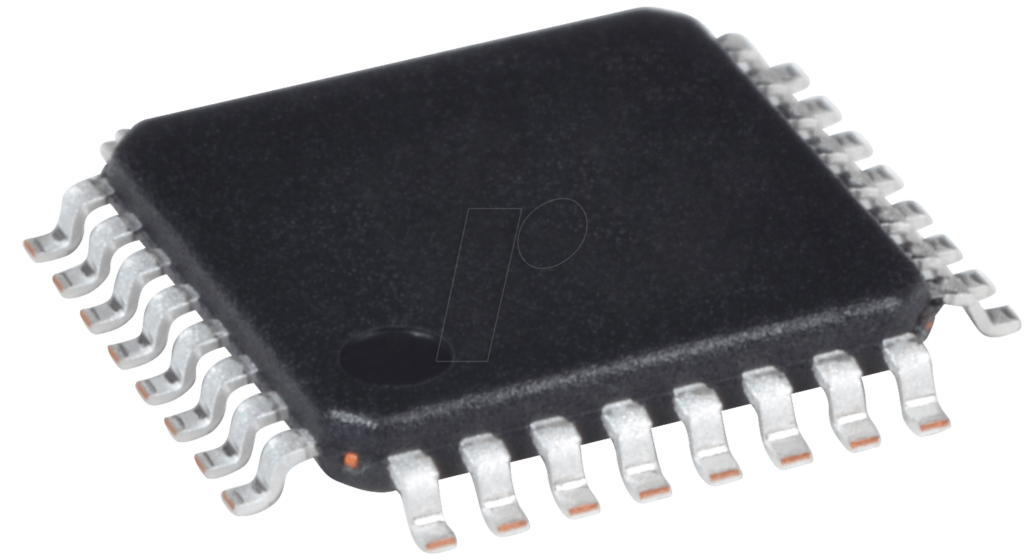

Reverse Engineering IC ATmega88PV Locked Flash

Reverse Engineering IC ATmega88PV Locked Flash

We can reverse engineering IC ATMEGA88PV locked flash, please view the IC ATMEGA88PV features for your reference:

When a byte is being programmed into the Flash or EEPROM, reading the address location being programmed will give the value $FF. At the time the device is ready for a new byte, the programmed value will read correctly.

This is used to determine when the next byte can be written.

This will not work for the value $FF so when programming this value, the user will have to wait for at least tWD_PROG_FL before programming the next Flash byte, or tWD_PROG_EE before the next EEPROM byte if Reverse Engineering IC ATMEGA88PV Locked Flash.

As a chip-erased device contains $FF in all locations, programming of addresses that are meant to contain $FF can be skipped. This does not apply if the EEPROM is reprogrammed without chip-erasing the device.

In that case, data polling cannot be used for the value $FF and the user will have to wait at least tWD_PROG_EE before programming the next byte. See Table 30 for tWD_PROG_FL and tWD_PROG_EE values.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied when Reverse Engineering IC ATMEGA88PV Locked Flash.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note:

“Max” means the highest value where the pin is guaranteed to be read as low if reverse engineering IC locked flash.

“Min” means the lowest value where the pin is guaranteed to be read as high.

Although each I/O port can sink more than the test conditions (20 mA at VCC = 5V, 10 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed before reverse engineering IC locked flash:

1] The sum of all IOL, for all ports, should not exceed 100 mA. If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

Although each I/O port can source more than the test conditions (3 mA at VCC = 5V, 1.5 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed when reverse engineering IC locked flash:

1] The sum of all IOH, for all ports, should not exceed 100 mA. If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition if Reverse Engineering IC ATMEGA88PV Locked Flash.